# LT768x

# High Performance TFT-LCD Graphics Controller

# **Data Sheet**

**V4.0**

# **Contents**

| Ð  | Introduction 6              |                                                   |    |  |  |  |  |  |  |  |  |

|----|-----------------------------|---------------------------------------------------|----|--|--|--|--|--|--|--|--|

| O  | Inte                        | ernal Block Diagram                               | 6  |  |  |  |  |  |  |  |  |

| 0  | Sys                         | stem Block Diagram                                | 7  |  |  |  |  |  |  |  |  |

| 0  | Мо                          | del Name                                          | 7  |  |  |  |  |  |  |  |  |

| 0  | Features 8                  |                                                   |    |  |  |  |  |  |  |  |  |

| 0  | Pin                         | Pin Assignment                                    |    |  |  |  |  |  |  |  |  |

| 0  | Pin                         | Description 1 (LT7681/LT7683+/LT7686/128Pin-LQFP) | 12 |  |  |  |  |  |  |  |  |

| O  | Pin                         | Description 2 (LT7680/68Pin-QFN)                  | 19 |  |  |  |  |  |  |  |  |

| 0  | Ab                          | solute Maximum Ratings                            | 22 |  |  |  |  |  |  |  |  |

| 0  |                             | ctrical Characteristics                           |    |  |  |  |  |  |  |  |  |

| 0  |                             | atures                                            |    |  |  |  |  |  |  |  |  |

| 1. | Clo                         | ck and Reset                                      | 24 |  |  |  |  |  |  |  |  |

|    | 1.1                         | Clock                                             |    |  |  |  |  |  |  |  |  |

|    | 1.2                         | Reset                                             |    |  |  |  |  |  |  |  |  |

|    |                             | 1.2.1 Power-on Reset                              | 27 |  |  |  |  |  |  |  |  |

|    |                             | 1.2.2 External Reset                              |    |  |  |  |  |  |  |  |  |

|    |                             | 1.2.3 Software Reset                              | 27 |  |  |  |  |  |  |  |  |

| 2. | Ho                          | st Interface                                      | 28 |  |  |  |  |  |  |  |  |

|    | 2.1 Parallel Host Interface |                                                   |    |  |  |  |  |  |  |  |  |

|    | 2.2                         | Serial Host Interface                             |    |  |  |  |  |  |  |  |  |

|    | 2.3                         | Display Input Data Format                         |    |  |  |  |  |  |  |  |  |

|    |                             | 2.3.1 Input Data without Opacity (RGB)            |    |  |  |  |  |  |  |  |  |

|    |                             | 2.3.2 Input Data with Opacity (αRGB)              | 40 |  |  |  |  |  |  |  |  |

| 3. | Dis                         | play Memory                                       | 42 |  |  |  |  |  |  |  |  |

|    | 3.1                         | Display RAM Data Structure                        | 43 |  |  |  |  |  |  |  |  |

|    |                             | 3.1.1 8bpp Display Data (RGB 3:3:2)               | 43 |  |  |  |  |  |  |  |  |

|    |                             | 3.1.2 16bpp Display Data (RGB 5:6:5)              | 43 |  |  |  |  |  |  |  |  |

|    |                             | 3.1.3 24bpp Display Data (RGB 8:8:8)              | 43 |  |  |  |  |  |  |  |  |

|    |                             | 3.1.4 Index Display with Opacity (αRGB 2:2:2:2)   |    |  |  |  |  |  |  |  |  |

|    |                             | 3.1.5 12bpp Display with Opacity (αRGB 4:4:4:4)   |    |  |  |  |  |  |  |  |  |

|    | 3.2                         | Color Palette RAM                                 | 44 |  |  |  |  |  |  |  |  |

| 4. | LCI                         | OInterface                                        | 45 |  |  |  |  |  |  |  |  |

| 5. | Dis | olay Function                                     | 47 |  |  |  |  |  |

|----|-----|---------------------------------------------------|----|--|--|--|--|--|

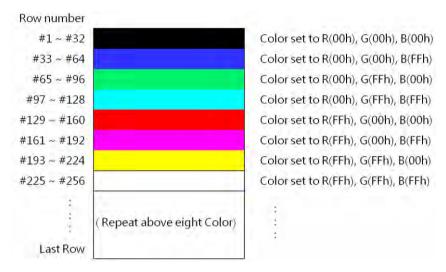

|    | 5.1 | Color Bar                                         | 47 |  |  |  |  |  |

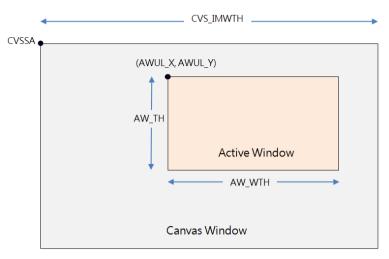

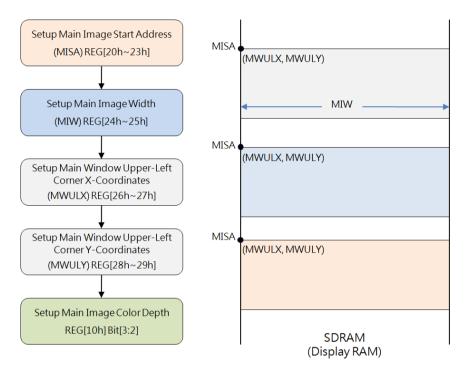

|    | 5.2 | Main Window                                       | 47 |  |  |  |  |  |

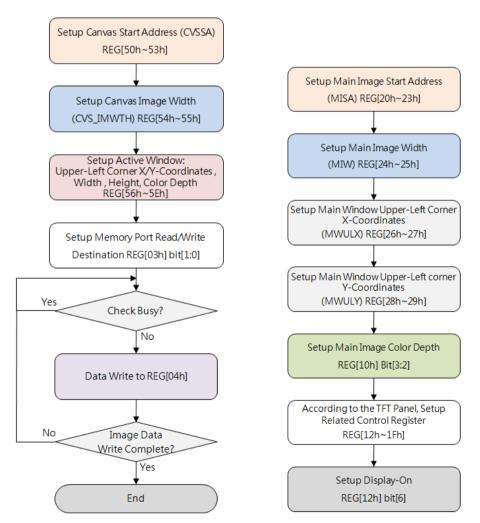

|    |     | 5.2.1 Configure Display Image Buffer              | 47 |  |  |  |  |  |

|    |     | 5.2.2 Write Image Data to Display Image Buffer    | 48 |  |  |  |  |  |

|    |     | 5.2.3 Display Main Window Image                   | 49 |  |  |  |  |  |

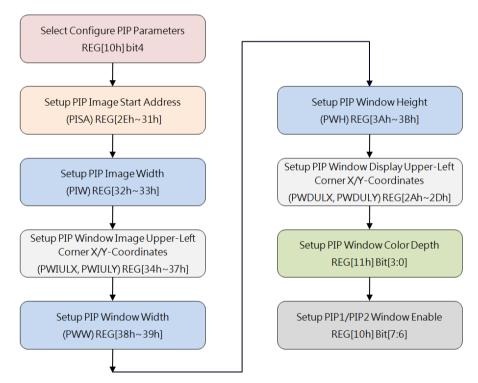

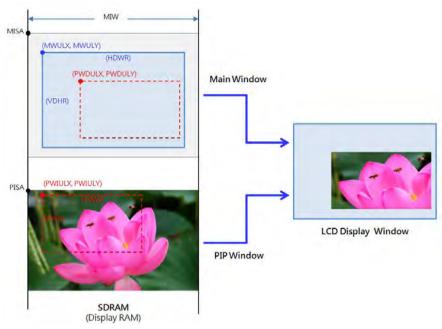

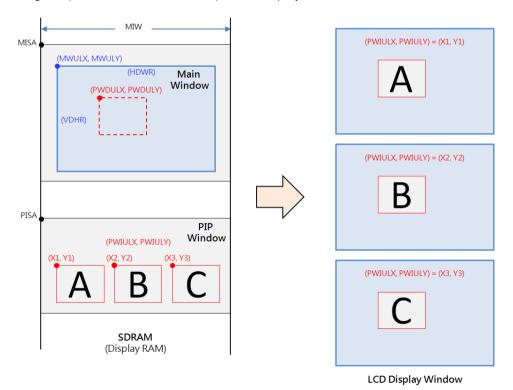

|    | 5.3 | Picture-In-Picture (PIP)                          | 50 |  |  |  |  |  |

|    |     | 5.3.1 PIP Window Setting                          | 50 |  |  |  |  |  |

|    |     | 5.3.2 PIP Display Position and PIP Image Position | 51 |  |  |  |  |  |

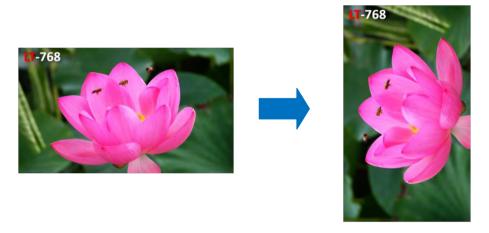

|    | 5.4 | Image Rotate and Mirror                           | 52 |  |  |  |  |  |

| 6. | Geo | ometric Drawing Engine                            | 55 |  |  |  |  |  |

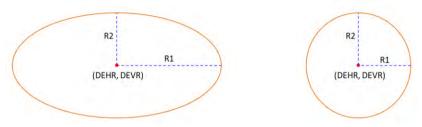

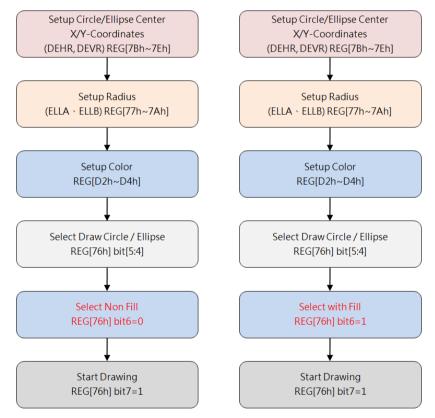

|    | 6.1 | Drawing Circle and Ellipse                        |    |  |  |  |  |  |

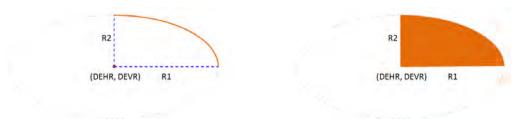

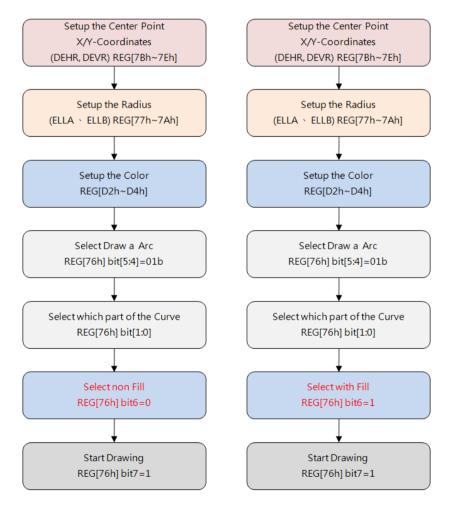

|    | 6.2 | Drawing Curve                                     |    |  |  |  |  |  |

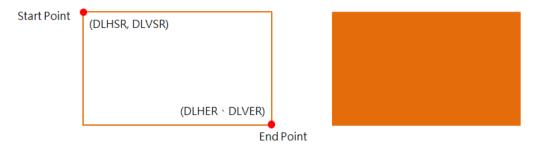

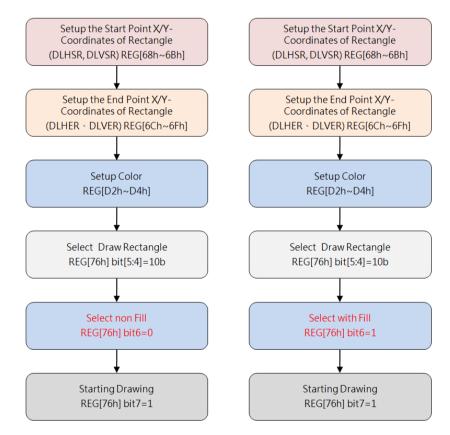

|    | 6.3 | Drawing Rectangle                                 |    |  |  |  |  |  |

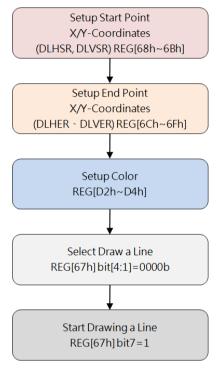

|    | 6.4 | Draw Line                                         | 58 |  |  |  |  |  |

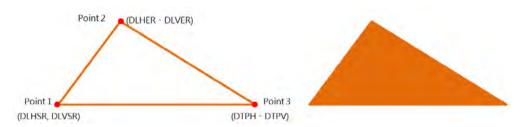

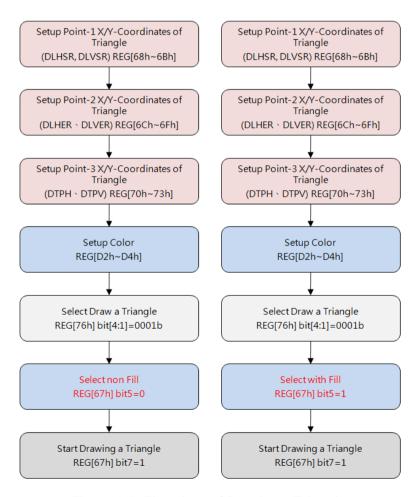

|    | 6.5 | Drawing Triangle                                  |    |  |  |  |  |  |

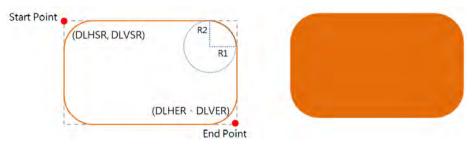

|    | 6.6 | Drawing Rounded-Rectangle                         | 60 |  |  |  |  |  |

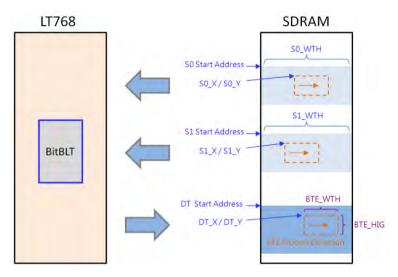

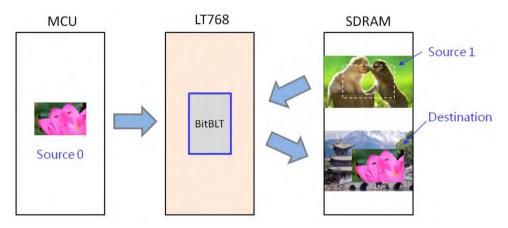

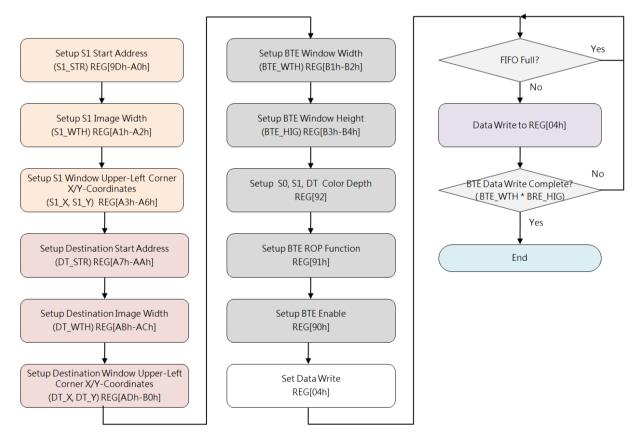

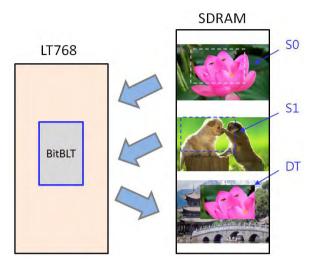

| 7. | Blo | ck Transfer Engine (BTE)                          | 61 |  |  |  |  |  |

|    | 7.1 | .1 BTE Basic Settings                             |    |  |  |  |  |  |

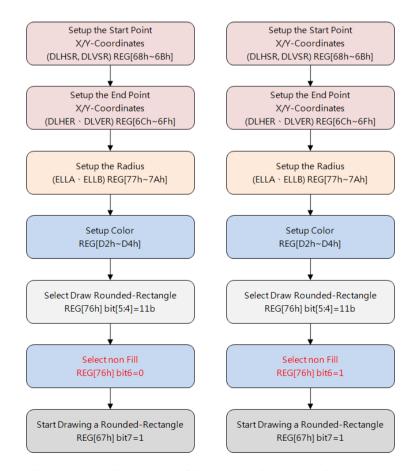

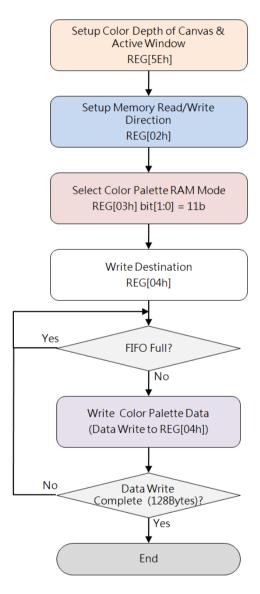

|    | 7.2 | Color Palette RAM                                 | 64 |  |  |  |  |  |

|    | 7.3 | BTE Operation Overview                            | 65 |  |  |  |  |  |

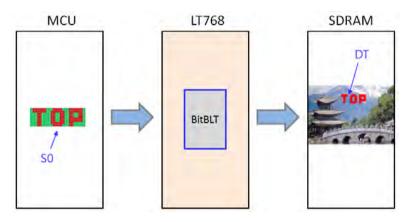

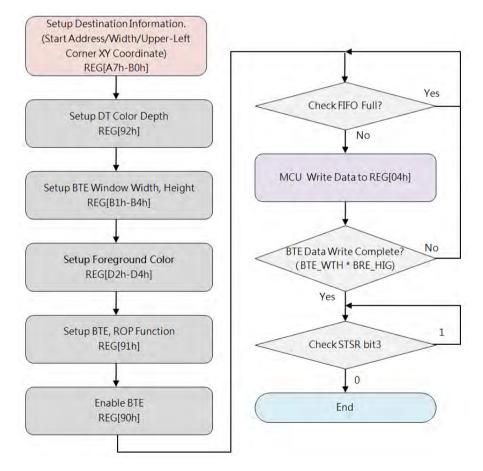

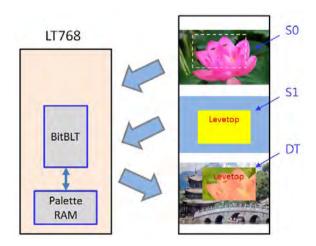

|    |     | 7.3.1 MCU Write with ROP                          |    |  |  |  |  |  |

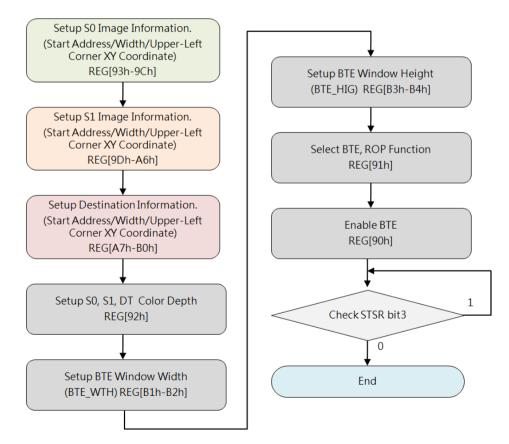

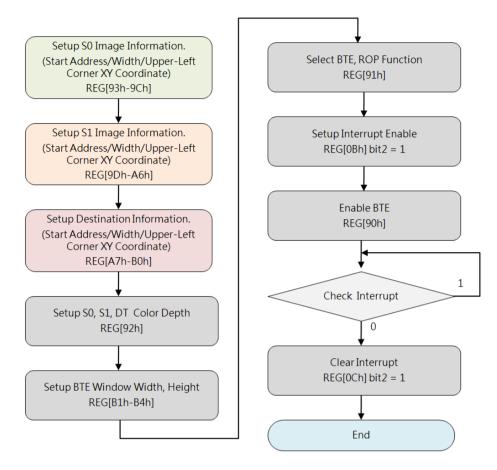

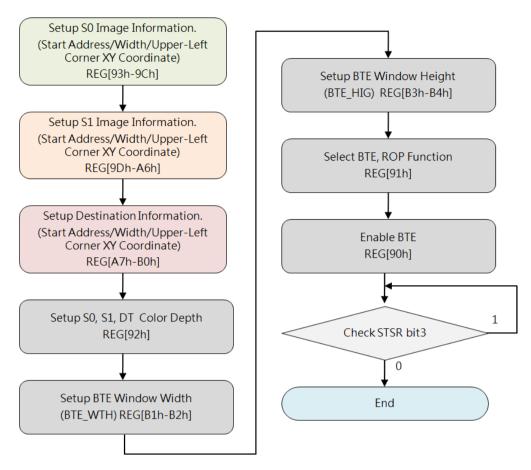

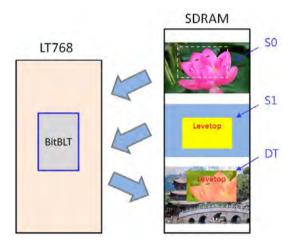

|    |     | 7.3.2 Memory Copy with ROP                        | 65 |  |  |  |  |  |

|    |     | 7.3.3 Solid Fill                                  | 65 |  |  |  |  |  |

|    |     | 7.3.4 Pattern Fill                                | 65 |  |  |  |  |  |

|    |     | 7.3.5 Pattern Fill with Chroma Key                | 65 |  |  |  |  |  |

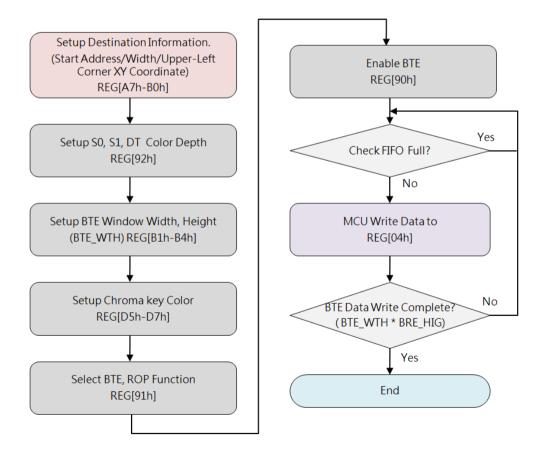

|    |     | 7.3.6 MCU Write with Chroma Key                   | 65 |  |  |  |  |  |

|    |     | 7.3.7 Memory Copy with Chroma Key                 | 65 |  |  |  |  |  |

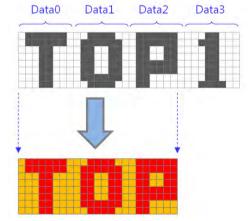

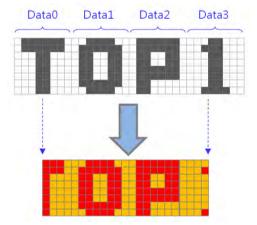

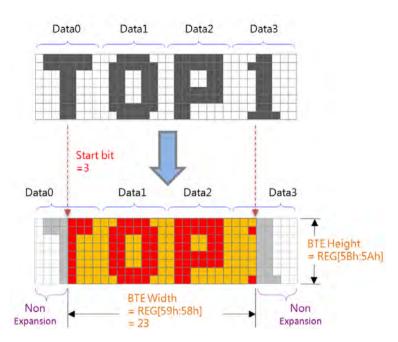

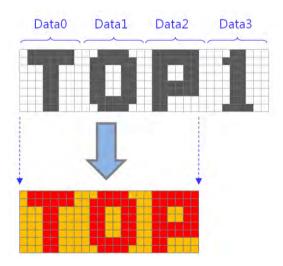

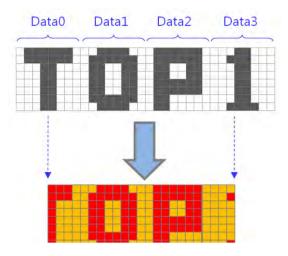

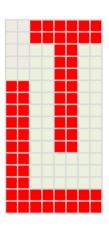

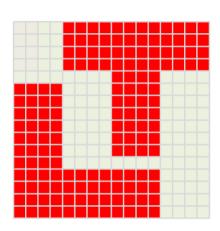

|    |     | 7.3.8 MCU Write with Color Expansion              | 65 |  |  |  |  |  |

|    |     | 7.3.9 Memory Copy with Color Expansion            | 66 |  |  |  |  |  |

|    |     | 7.3.10 Memory Copy with Opacity                   | 66 |  |  |  |  |  |

|    |     | 7.3.11 MCU Write with Opacity                     | 66 |  |  |  |  |  |

|    | 7.4 | BTE Memory Access Method                          | 67 |  |  |  |  |  |

|    | 7.5 | BTE Chroma Key (Transparency Color) Function      |    |  |  |  |  |  |

|    | 7.6 | BTE Operation Detail                              |    |  |  |  |  |  |

|    |     | 7.6.1 MCU Write with ROP                          | 68 |  |  |  |  |  |

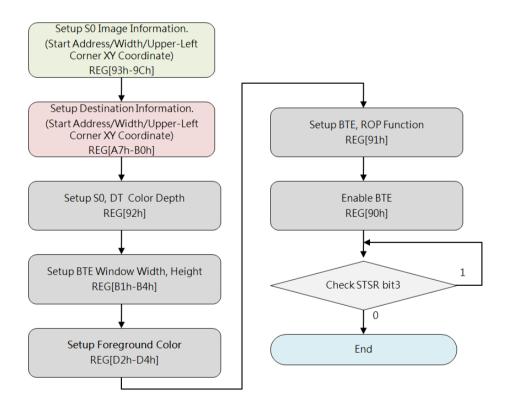

|    |     | 7.6.2 Memory Copy (move) with ROP                 | 69 |  |  |  |  |  |

|    |            | 7.6.3 MCU Write with Chroma Key (w/o ROP)              | 71  |

|----|------------|--------------------------------------------------------|-----|

|    |            | 7.6.4 Memory Copy with Chroma Key (w/o ROP)            | 72  |

|    |            | 7.6.5 Pattern Fill with ROP                            | 73  |

|    |            | 7.6.6 Pattern Fill with Chroma Key                     | 74  |

|    |            | 7.6.7 MCU Write with Color Expansion                   | 75  |

|    |            | 7.6.8 MCU Write with Color Expansion and Chroma key    | 78  |

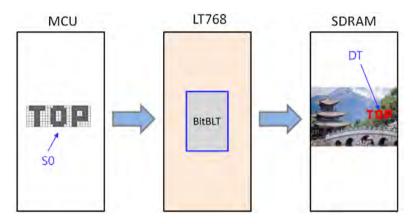

|    |            | 7.6.9 Memory Copy with Opacity                         | 79  |

|    |            | 7.6.10 MCU Write with Opacity                          | 83  |

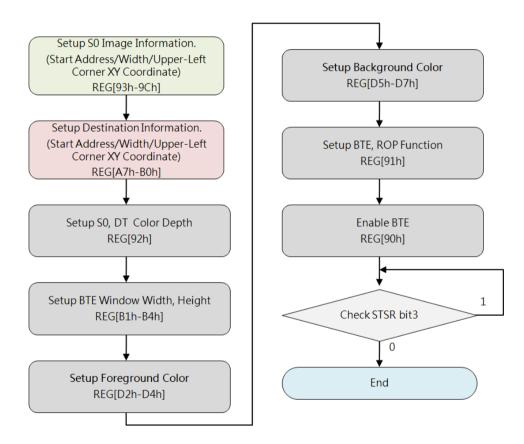

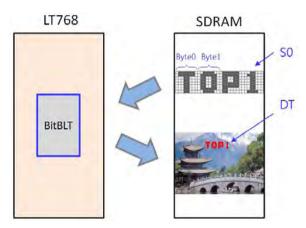

|    |            | 7.6.11 Memory Copy with Color Expansion                | 84  |

|    |            | 7.6.12 Memory Copy with Color Expansion and Chroma Key | 86  |

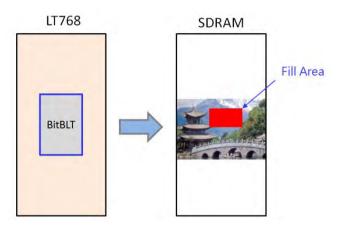

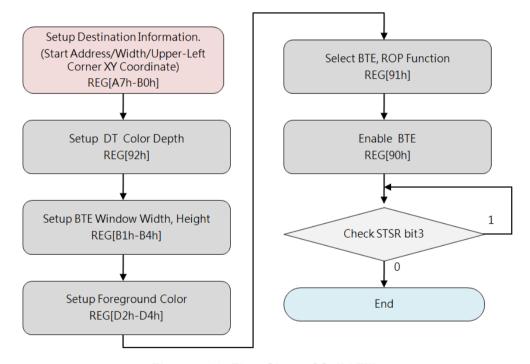

|    |            | 7.6.13 Solid Fill                                      | 87  |

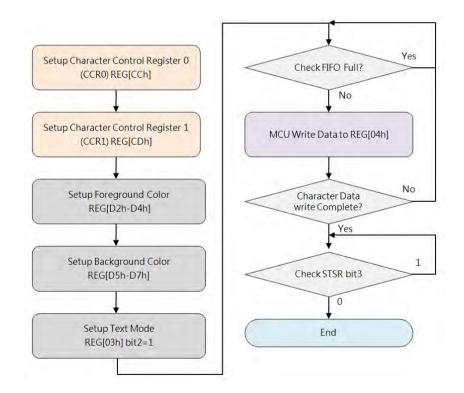

| 8. | Disp       | olay Text                                              | 88  |

|    | 8.1        | Internal CGROM                                         | 88  |

|    | 8.2        | User-defined Character Graphic (UCG)                   |     |

|    |            | 8.2.1 8*16 UCG Data Format                             | 91  |

|    |            | 8.2.2 16*16 UCG Data Format                            | 92  |

|    |            | 8.2.3 12*24 UCG Data Format                            | 93  |

|    |            | 8.2.4 24*24 UCG Data Format                            | 94  |

|    |            | 8.2.5 16*32 UCG Data Format                            | 95  |

|    |            | 8.2.6 32*32 UCG Data Format                            | 96  |

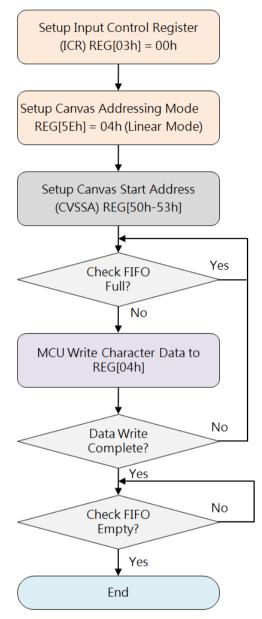

|    |            | 8.2.7 Initialize CGRAM from MCU                        | 97  |

|    |            | 8.2.8 Initialize CGRAM from Serial Flash               | 98  |

|    | 8.3        | Character Rotation by 90 Degree                        | 99  |

|    | 8.4        | Size Enlargement                                       |     |

|    | 8.5        | Background Transparency                                |     |

|    | 8.6        | Character Full-Alignment                               |     |

|    | 8.7<br>8.8 | Automatic Line Feed  Cursor                            |     |

|    | 0.0        | 8.8.1 Text Cursor                                      |     |

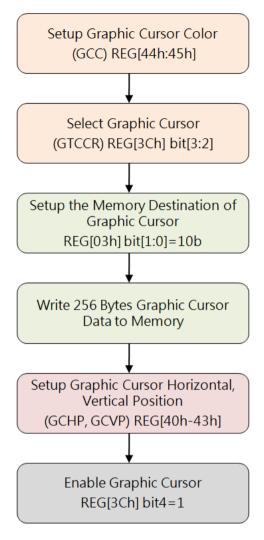

|    |            | 8.8.2 Graphic Cursor                                   |     |

| 9. | Puls       | e Width Modulation (PWM)                               | 105 |

|    | 9.1        | PWM Clock Source                                       |     |

|    | 9.2        | PWM Output                                             |     |

| 10 | .Seri      | al Bus Master                                          | 108 |

|    | 10.1       | Power-on Display                                       | 108 |

|    | 10.2       | SPI Master                                             | 112 |

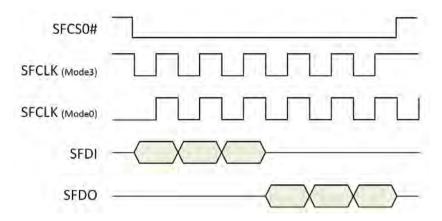

|    | 10.3       | Serial Flash Controller                                | 114 |

|    |            | LT768x_DS_ENG / V4.0                                   |     |

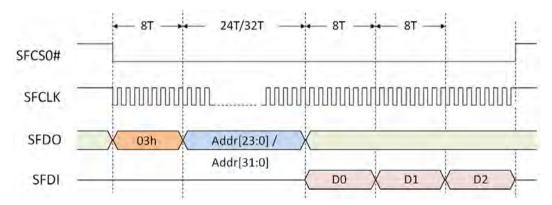

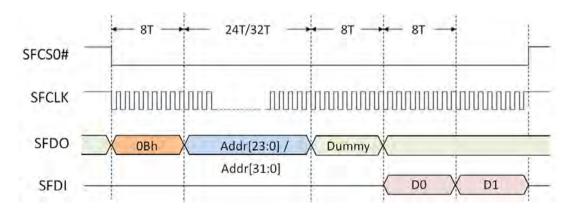

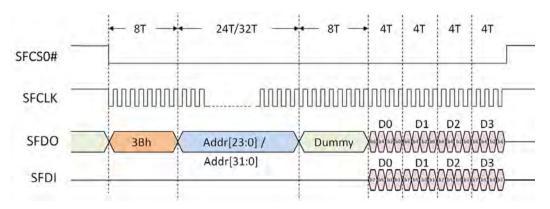

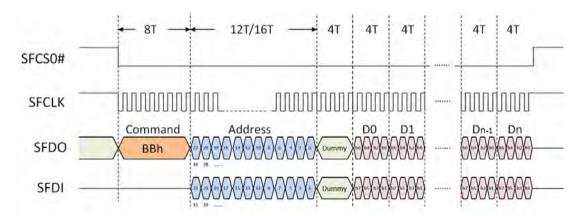

|        | 10.3.1 External Serial Flash                        | 117 |

|--------|-----------------------------------------------------|-----|

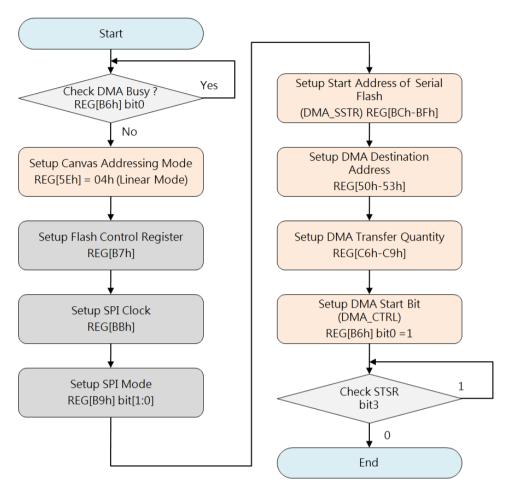

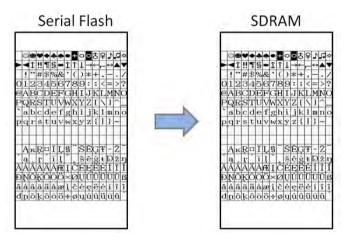

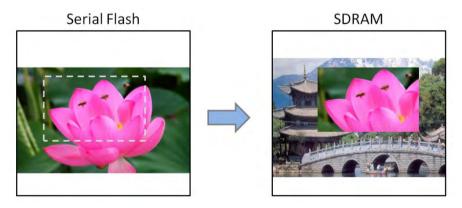

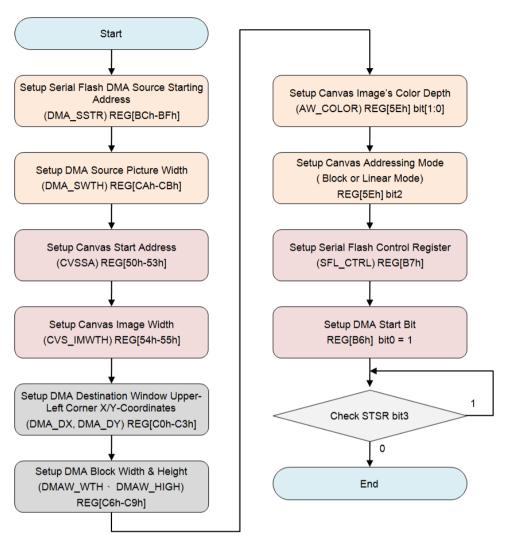

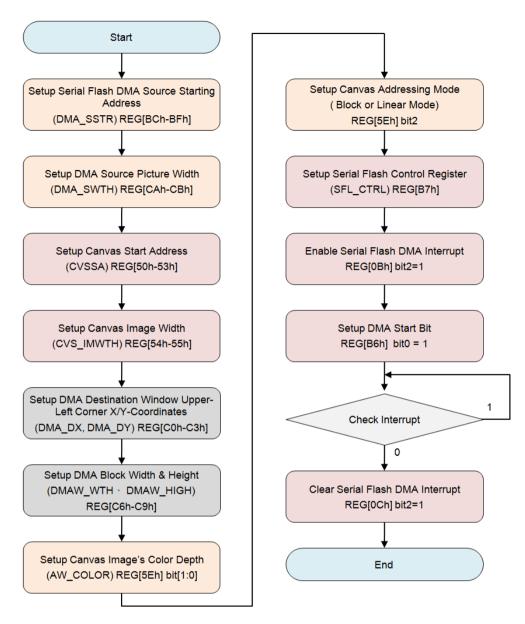

|        | 10.3.2 DMA in Linear Mode for External Serial Flash | 118 |

|        | 10.3.3 DMA in Block Mode for External Serial Flash  | 118 |

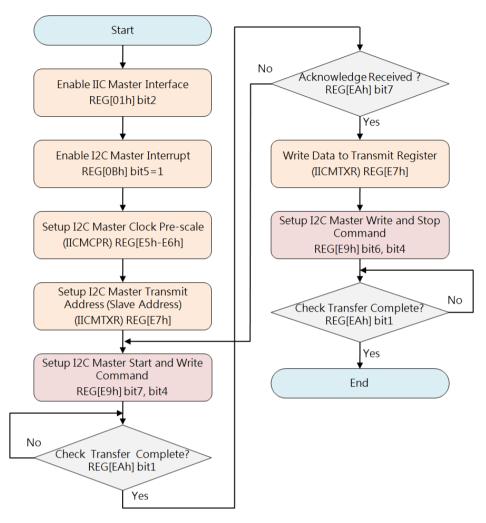

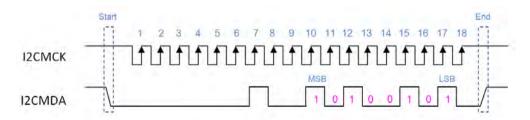

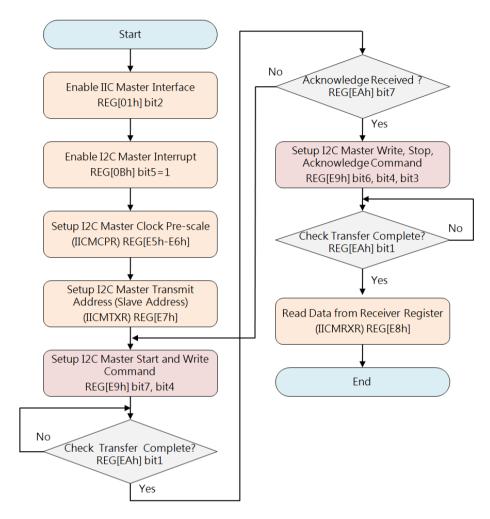

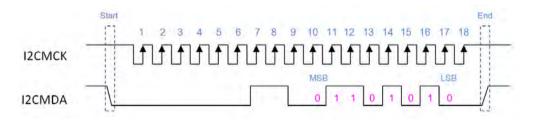

| 10.4   | I2C Master                                          | 121 |

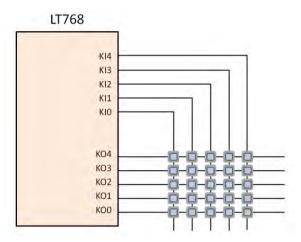

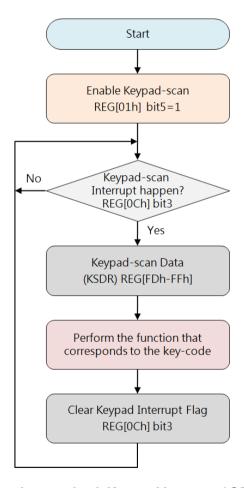

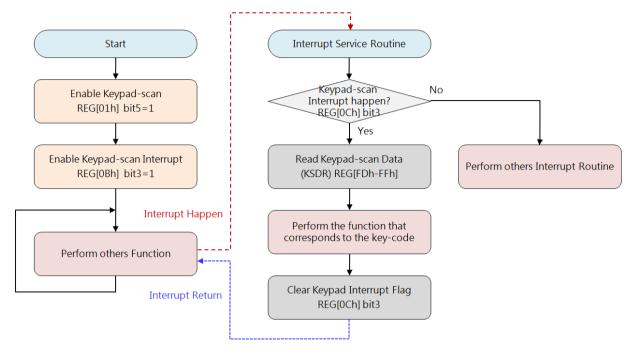

| 11.Key | /pad-Scan                                           | 124 |

| 11.1   | Keypad-scan Operation                               | 124 |

| 12.GP  | O Interface                                         | 128 |

| 13.Po\ | wer Management                                      | 129 |

| 13.1   | Normal Mode                                         | 129 |

|        | 2 Standby Mode                                      |     |

|        | Suspend Mode                                        |     |

| 13.4   | Sleep Mode                                          | 130 |

| 14.Reg | gister Description                                  | 131 |

| 14.1   | Status Register                                     | 131 |

| 14.2   | 2 Configuration Registers                           | 133 |

| 14.3   | PLL Setting Register                                | 138 |

| 14.4   | Interrupt Control Register                          | 140 |

| 14.5   | LCD Display Control Registers                       | 145 |

| 14.6   | Geometric Engine Control Registers                  | 156 |

| 14.7   | ' PWM Control Registers                             | 165 |

| 14.8   | Bit Block Transfer Engine (BTE) Control Registers   | 168 |

| 14.9   | Serial Flash & SPI Master Control Registers         | 176 |

| 14.1   | 0 Text Engine Registers                             | 182 |

| 14.1   | 1Power Management Control Register                  | 187 |

| 14.1   | 2 Display RAM Control Register                      | 188 |

| 14.1   |                                                     |     |

| 14.1   | 4 GPIO Register                                     | 194 |

| 14.1   | 5 Keypad-scan Control Register                      | 196 |

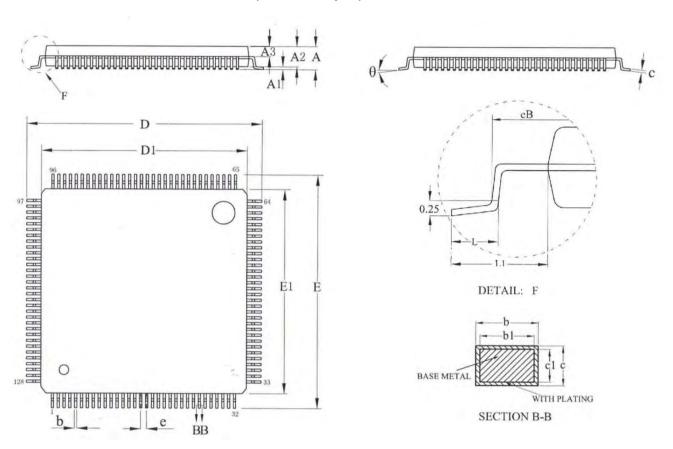

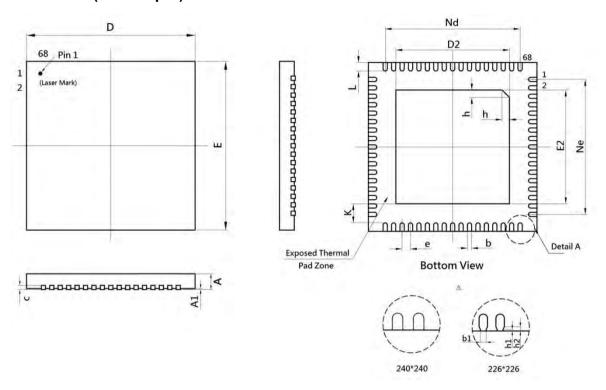

| Pa     | ckage Information                                   | 198 |

| _      | vision                                              |     |

| _      | pyright                                             | 200 |

|        |                                                     |     |

# High Performance TFT-LCD Graphics Controller

# Introduction

LT768x are a series high-performance TFT-LCD graphics accelerated display chip. Its main function is to assist MCU to display the contents of the TFT screen to the TFT Driver. It provides graphics acceleration, PIP (picture-in-picture), geometry graphics and other functions, in addition to enhance the display efficiency, also greatly reduces the MCU processing graphics display time spent. LT768x also supports a very broad display resolution, can be from 320\*240(QVGA) to 1280\*1024(SXGA), the display is supported 16/18/24bits RGB interface.

LT768x supports a variety of MCU interface, including SPI, I2C serial port, or 8-bit, 16-bit parallel interface. In order to achieve multi-layers high-resolution display effect, LT768x embedded a 128MB Display RAM.

This Displays Memory can support 16M color display from 2 gray to 1bit per pixel to up to 24bits per pixel. At the same time to reduce the animation display MCU in the software operation burden. LT768x built-in geometry drawing engine, supporting the painting point, drawing Line, drawing curve, ellipse, triangle, rectangle, rounded rectangle and other functions. The embedded hardware graphics Acceleration Engine (BTE) provides the command type of graphics operations, such as display rotation, mirror shot, the painting (PIP/Master-Sub Screen) and graphics mixed transparent display and other functions, enhance the display of the product performance, so can greatly reduce the MCU software operating burden. if use the high-speed SPI interface, then it can reduce the MCU I/O port needs, without to upgrade the MCU for TFT display. LT768x powerful display function is very suitable for the electronic products with TFT-LCD screen, such as home appliances, multi-functional business machines, industrial equipment, industrial control, electronic equipment, medical equipment, human-computer interface, testing equipment and other products.

# Internal Block Diagram

Figure A-1: Internal Block Diagram

LT768x DS ENG / V4.0

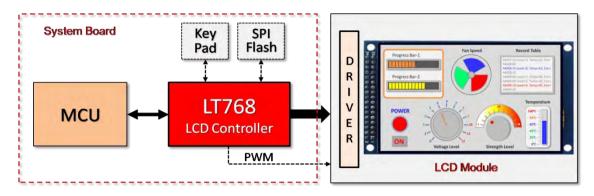

# System Block Diagram

Figure A-2: LT768x Designed on System Board

Figure A-3: LT768x Designed on TFT-LCD Module

# Model Name

**Table A-1: Model Selection**

| Model Name | Package      | Embedded<br>Display RAM | Resolution | Colors     |

|------------|--------------|-------------------------|------------|------------|

| LT7681     | LQFP-128     | 128Mb                   | 640*480    | 16.7M      |

| LT7683+    | LQFP-128     | 128Mb                   | 1024*768   | 16.7M      |

| LT7686     | LQFP-128     | 128Mb                   | 1280*1024  | 16.7M      |

| LT7680A-R  | QFN-68 (8*8) | 128Mb                   | 1280*1024  | 65K / 262K |

| LT7680B-R  | QFN-68 (8*8) | 128Mb                   | 480*320    | 65K / 262K |

# Features

#### **Host Interface**

- Support Three Types 8/16bits Asynchronous Bus Register Interface (or Memory Data)

- > Indirect Intel-80 Bus Interface

- ➤ Indirect Motorola-6800 Bus Interface

- Provides Insert Wait State Mechanism on Parallel Host Cycle

- Support I<sup>2</sup>C Bus Interface

- Support Various SPI Protocol. Ex. 3 or 4-wire SPI

### **Display Data Formats**

- 1bpp: Monochrome Data (1-bit/Pixel)

- 8bpp: RGB 3:3:2 (1-byte/Pixel)

- 16bpp: RGB 5:6:5 (2-byte/Pixel)

- 24bpp: RGB 8:8:8 (3-byte/Pixel or 4-byte/Pixel)

- Index 2:6 (64 Index Colors/Pixel with Opacity Attribute)

- αRGB 4:4:4:4 (4096 Colors/Pixel with Opacity Attribute)

### **Support Panel and Resolution**

- Support 16/18/24-bits RGB Interface Type Panel

- Supported Resolution:

> QVGA : 320\*240, 16/18/24-bit LCD Panel

> WQVGA: 480\*272, 16/18/24-bit LCD Panel

> VGA : 640\*480, 16/18/24-bit LCD Panel

> WVGA : 800\*480, 16/18/24-bit LCD Panel

> SVGA : 800\*600, 16/18/24-bit LCD Panel

> QHD : 960\*540, 16/18/24-bit LCD Panel

> WSVGA: 1024\*600, 16/18/24-bit LCD Panel

> XGA : 1024\*768, 16/18/24-bit LCD Panel

> SXGA : 1280\*1024, 16/18/24-bit LCD Panel

### **Display Functions**

- Multiple Display Buffer: Multi buffering allows the main display window to be switched among buffers. Multi buffering allows a simple animation display to be performed by switching the buffers

- Horizontal/Vertical Flip Display: Vertical Flip display functions are available for image data reads. PIP window will be disabled if flip display function enable

- Mirror and Rotation Functions are Available for Image Data Writes

- Provide four User-defined 32\*32 Pixels Graphic Cursor

- Virtual Display: Virtual display is available to show an image which is larger than LCD panel size. The image may scroll easily in any direction

- Picture-in-Picture (PIP) Display: Supported two PIP windows area: Enabled PIP windows are always displayed on top of Main window. The PIP1 window is always on top of PIP2 window

- Wake-up Display: Wake-up Display is available to show the display data quickly which data is stored in Display RAM. This feature is used when returning from the Standby mode or Suspend mode

- Initial Display: Embedded a tiny processor with 12 instructions and use to show display data which stored in the serial flash and need not external MPU participate. It will auto execute after power-on, until program execute complete then handover control rights to external MCU

- Color Bar: It could display color bar on panel directly. Default resolution is 640 dots by 480 dots

#### **Bit Block Transfer Engine (BTE)**

- 2D BTE Engine

- Copy Image with Raster Operators

- Color Depth Conversion

- Solid Fill & Pattern Fill

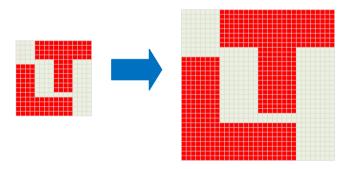

- Provide User-defined Patterns with 8\*8 Pixels or 16\*16 Pixels

- Opacity (Alpha-Blend) Control: It blends two images and then generates a new image

- Chroma-Keying Function: Mixes images with applying the specified RGB color according to transparency rate

- Window Alpha-Blending Function: Mixes two images according to transparency rate in the specified region (fade-in and fade-out functions are available)

- Dot Alpha-Blending Function: Mixes images according to transparency rate when the target is a graphics image in the RGB format

### **Display RAM (Frame Buffer)**

- LT7680A-R / 7680B-R: Embedded 128Mb Display RAM

- LT7681 / 7683+ / 7686: Embedded 128Mb Display RAM

## **Shape Drawing Engine**

■ Provide Smart Drawing Features: Line, Rectangle, Triangle, Polygon, Poly-Line, Circle, Ellipse, Arc, Rounded-Rectangle and Circle-Rectangle

#### **Text Features**

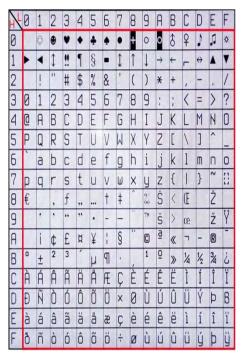

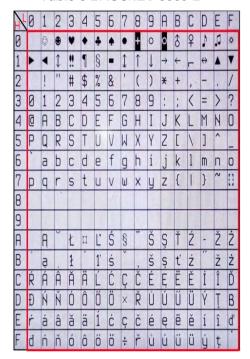

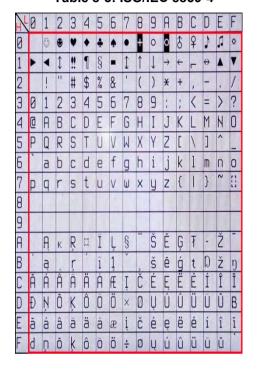

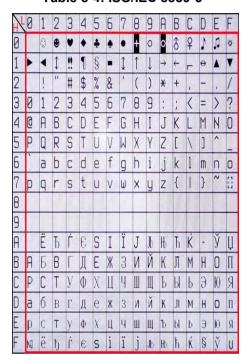

- Embedded 8\*16, 12\*24, 16\*32 Character Sets of ISO/IEC 8859-1/2/4/5

- User-defined Characters Support Half Size & Full Size for 8\*16, 12\*24 and 16\*32

- Programmable Text Cursor for Writing with Character

- Character Enlargement Function \*1, \*2, \*3, \*4 for Horizontal/Vertical Direction

- Support Character Rotates 90 Degree

#### **PWM Interface**

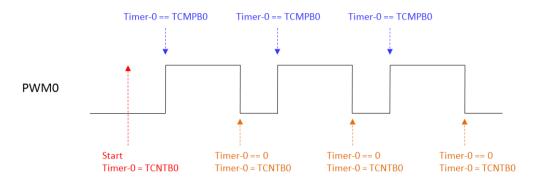

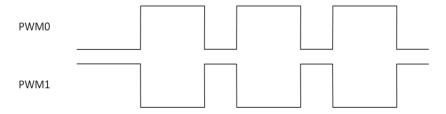

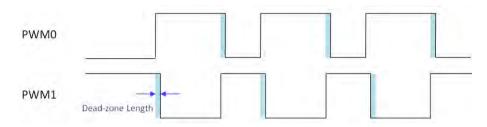

- Embedded Two 16bits Timers

- One 8-bit Pre-Scalars & One 4bits Divider

- Programmable Duty Control of Output Waveform (PWM)

- Auto Reload Mode or One-Shot Pulse Mode

- Dead-Zone Generator

#### **SPI Master Interface**

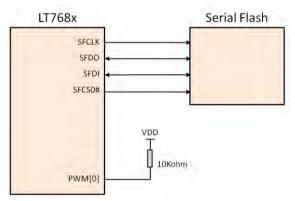

- Provide DMA Function: Support Direct Data Transfer from External Serial Flash to Frame Buffer

- Compatible with Standard SPI Specifications

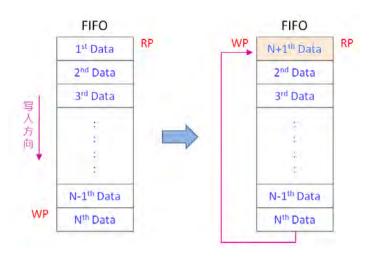

- Provides 16bytes Read FIFO and 16bytes Write FIFO

- Provide Interrupt when Tx FIFO was Empty and SPI Tx/Rx Engine Idle

#### **I2C Interface**

■ Support Standard Mode (100kbps) and Fast Mode (400kbps)

#### **Key-Matrix Interface**

- Support up to 5\*5 key matrix

- Programmable Scan Period

- Support Long Key & Repeat Key

- Support up to Two Keys Pressed Simultaneously

- Support Keypad-Scan Wakeup function

### **Power Saving**

- Support Three Kind of Power Saving Mode: Standby, Suspend and Sleep Mode

- Support Wakeup Function by Host and External Event

#### **Clock Source**

■ Embedded Programmable PLL for Core Clock, LCD Panel's Pixel Clock and Frame Buffer Clock

#### Reset

- Provide Power On Reset Automatically

- Accept External Hardware Reset to Synchronize with System

- Software Command Reset

#### **Power Supply**

- VDD: 3.3V +/- 0.3V

- Embedded 1.8V LDO

#### **Package**

■ LQFP 100/128-Pins, QFN 68-Pins

#### **Temperature**

■ -40°C~85°C

# Pin Assignment

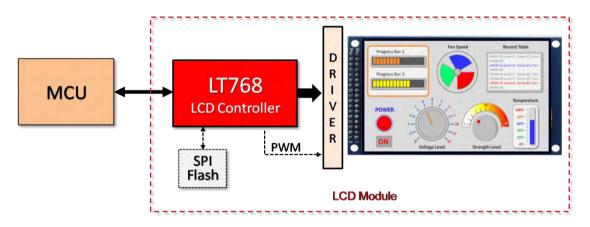

Figure A-4: LT7681/LT7683+/LT7686 Pin Assignment (LQFP-128Pin)

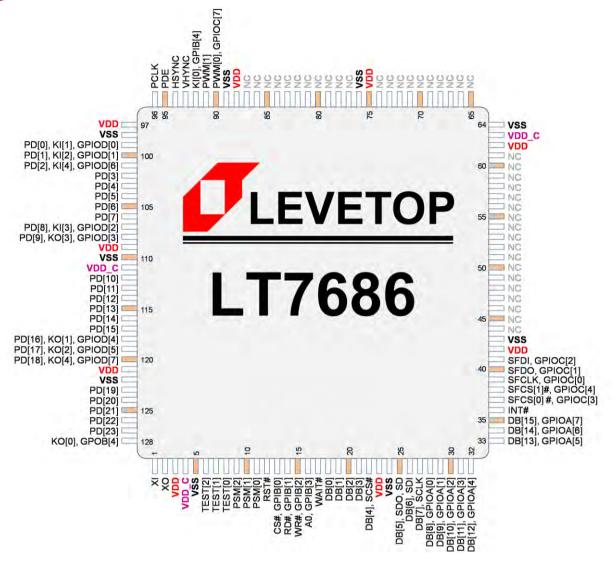

Figure A-5: LT7680A-R / LT7680B-R Pin Assignment (QFN-68Pin)

# Pin Description -1 (LT7681/LT7683+/LT7686/128Pin-LQFP)

LT7681/7683+/7686 are 128Pin LQFP type package. The following tables are pin description of these chips.

### **Host Interface Select Signals (3 Pins)**

Table A-2: Host I/F Select Signals

| Pin# | Pin Name | I/O |         |                                  | Pin Description                                   |  |                                       |                                              |

|------|----------|-----|---------|----------------------------------|---------------------------------------------------|--|---------------------------------------|----------------------------------------------|

|      |          |     | Host II | nterface Sele                    | ection                                            |  |                                       |                                              |

|      |          | 1   |         | PSM[2:0]                         | Host I/F Mode                                     |  |                                       |                                              |

|      |          |     |         |                                  |                                                   |  | 0 0 X 8bits or 16bits 8080 Paral Mode | 8bits or 16bits 8080 Parallel Interface Mode |

| 9~11 | PSM[2:0] |     |         | 0 1 X                            | 8bits or 16bits 6800 Parallel Interface Mode      |  |                                       |                                              |

|      |          |     |         | 100                              | 3-Wire SPI Mode                                   |  |                                       |                                              |

|      |          |     |         | 101                              | 4-Wire SPI Mode                                   |  |                                       |                                              |

|      |          |     |         | 11X                              | I2C Mode                                          |  |                                       |                                              |

|      |          |     |         | t interface s<br>al interrupt in | set as parallel mode, then PSM[0] pin is put pin. |  |                                       |                                              |

### **Host Parallel I/F Signals (22 Pins)**

Table A-3: Host Parallel I/F Signals

| Pin#            | Pin Name             | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35~25,<br>22~18 | DB[15:0]             | Ю   | Host Data Bus  These are data bus for data transfer between Host and LT768x.  DB[15:8] will become GPIO (GPIOA[7:0]) when parallel Host 8080/6800 16-bits data bus mode doesn"t set.  DB[7:0] are multiplex pins that share with Serial Host control pins. When serial host mode set then DB[7:0] are defined as the control pins of serial host. Please refer to Host Interface section. |

| 13              | CS#<br>GPIB[0]       | I   | Chip Select Input Low active chip select pin from Host. If host interface set as serial host mode, then this pin can be set as GPIB[0]. This pin with an internal pull-high resistor.                                                                                                                                                                                                     |

| 14              | RD#<br>EN<br>GPIB[1] | I   | Read / Enable Input RD#: When host interface is 8080 mode then this is a Read input signal, active low. EN: When interface is 6800 mode then this is a Enable input signal, active high. If host interface set as serial host mode then this pin can be set as GPIB[1]. This pin with an internal pull-high resistor.                                                                     |

| Pin# | Pin Name              | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | WR#<br>RW#<br>GPIB[2] | I   | Write / Read-Write Input WR#: When host interface is 8080 mode then this is a Write input signal, active low. RW#: When interface is 6800 mode then this is a Read-Write input signal. It active high in "Host's read cycle, and active low in Host's write cycle. If host interface set as serial host mode then this pin will be set as GPIB[2]. This pin with an internal pull-high resistor. |

| 16   | A0<br>GPIB[3]         | I   | Command / Data Select Input  The pin is used to select Command or Data cycle.  A0 = 0, Status Read or Command Write cycle is selected.  A0 = 1, Data Read or Data Write cycle is selected.  If host interface set as serial host mode then this pin will be set as GPIB[3]. This pin with an internal pull-high resistor.                                                                        |

| 36   | INT#                  | 0   | Interrupt Output Signal The interrupt output for host to indicate the status.                                                                                                                                                                                                                                                                                                                    |

| 17   | WAIT#                 | 0   | Wait Output Signal When high, it indicates that the LT768x is ready to transfer data. When low, then microprocessor is in wait state.                                                                                                                                                                                                                                                            |

# MCU Serial I/F Signals (8 Pins)

Table A-4: Host Serial I/F Signals

| Pin# | Pin Name                        | I/O | Pin Description                                                                                                                                                                                                                                                                                      |

|------|---------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27   | SCLK<br>(DB[7])                 | ı   | SPI or I2C Clock SCLK: Clock of 3-wire, 4-wire Serial or I2C interface. This is a multiplex pin that share with Parallel Host Data Bus DB[7].                                                                                                                                                        |

| 26   | SDI<br>I2C_SDA<br>(DB[6])       | I   | I2C Data / 4-wire SPI Data Input SDI: Data input pin of 4-wire SPI I/F. Connect to MCU's MOSI. I2C_SDA: Bi-direction data pin of I2C I/F. This pin is not used In 3-Wire serial I/F. Please connect it to GND. This is a multiplex pin that share with Parallel Host Data Bus DB[6].                 |

| 25   | SD<br>SDO<br>I2CA[5]<br>(DB[5]) | Ю   | 3-wire SPI Data / 4-wire SPI Data Output / I2C Slave Address Select SD: Bi-direction data pin of 3-wire SPI I/F. SDO: Data output pin of 4-wire SPI I/F. Connect to MCU's MISO. I2CA[5]: I2C device address bit[5] of I2C I/F. This is a multiplex pin that share with Parallel Host Data Bus DB[5]. |

Table A-4: Host Serial I/F Signals (Continued)

| Pin#  | Pin Name               | I/O | Pin Description                                                                                                                                                                                                         |

|-------|------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22    | SCS# I2CA[4] (DB[4])   | I   | SPI Chip Select / I2C Slave Address Select SCS#: Chip select pin for 3-wire or 4-wire serial I/F. I2CA[4]: I2C device address bit[4]. This is a multiplex pin that share with Parallel Host Data Bus DB[4].             |

| 21~18 | I2CA[3:0]<br>(DB[3:0]) | I   | I2C Slave Address Select I2CA[3:0]: I2C device address bit [3:0]. These pins are not used In 3-Wire or 4-Wire I/F. Please connect them to GND. These are multiplex pins that share with Parallel Host Data Bus DB[3:0]. |

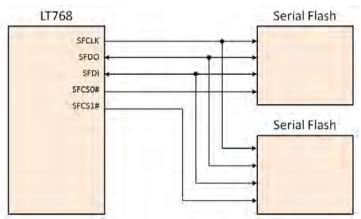

# **External Serial Flash / SPI Master Signals (5 Pins)**

**Table A-5: External Serial Flash Signals**

| Pin# | Pin Name             | I/O | Pin Description                                                                                                                                                                                                                                                                                                    |

|------|----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37   | SFCS[0]#<br>GPIOC[3] | Ю   | Chip Select 0 for External Serial Flash or SPI device SPI Chip select pin #0 for serial Flash or SPI device. If SPI master I/F is disabled then it can be programmed as GPIOC[3], and default is input function.                                                                                                   |

| 38   | SFCS[1]#<br>GPIOC[4] | Ю   | Chip Select 1 for External Serial Flash or SPI device SPI Chip select pin #1 for serial Flash or SPI device. If SPI master I/F is disabled then it can be programmed as GPIOC[4], and default is input function.                                                                                                   |

| 39   | SFCLK<br>GPIOC[0]    | Ю   | SPI Serial Clock Serial clock output for serial Flash/ROM or SPI device. If SPI master I/F is disabled then it can be programmed as GPIO C[0], and default is input function.                                                                                                                                      |

| 40   | SFDO<br>GPIOC[1]     | Ю   | Master Output Slave Input Single Mode: Data input of serial Flash or SPI device. For LT768, it is output.  Dual Mode: The signal is used as bi-direction data #0(SIO0). Only valid in serial flash DMA mode.  If SPI master I/F is disabled then it can be programmed as GPIO C[1], and default is input function. |

| 41   | SFDI<br>GPIOC[2]     | Ю   | Master Input Slave Output Single Mode: Data output of serial Flash or SPI device. For LT768, it is input.  Dual Mode: The signal is used as bi-direction data #1(SIO1). Only valid in serial flash DMA mode.  If SPI master I/F is disabled then it can be programmed as GPIOC[2], and default is input function.  |

# **LCD Driver Signals (28 Pins)**

**Table A-6: LCD Driver Signals**

| Pin#               | Pin Name | I/O | Pin Description |             |               |                  |                 |                                     |  |

|--------------------|----------|-----|-----------------|-------------|---------------|------------------|-----------------|-------------------------------------|--|

|                    |          |     | TF1             | C/256K/16.7 | a bus outpu   | epth by re       | egister sett    | T76x suppor<br>ing; user ca<br>ing. |  |

|                    |          |     |                 | Pin         |               | TFT-LCD          | Interface       |                                     |  |

|                    |          |     |                 | Name        | 11b<br>(GPIO) | 10b<br>(16bits)  | 01b<br>(18bits) | 00b<br>(24bits)                     |  |

|                    |          |     |                 | PD[0]       | GF            | PIOD[0] / KI     |                 | В0                                  |  |

|                    |          |     |                 | PD[1]       | GF            | PIOD[1] / KI     | [2]             | B1                                  |  |

|                    |          |     |                 | PD[2]       | GPIOD[        | 6] / KI[4]       | В0              | B2                                  |  |

|                    |          |     |                 | PD[3]       | GPIOE[0]      | В0               | B1              | В3                                  |  |

|                    |          |     |                 | PD[4]       | GPIOE[1]      | B1               | B2              | B4                                  |  |

|                    |          |     |                 | PD[5]       | GPIOE[2]      | B2               | В3              | B5                                  |  |

|                    |          |     |                 | PD[6]       | GPIOE[3]      | В3               | B4              | В6                                  |  |

|                    |          |     |                 | PD[7]       | GPIOE[4]      | B4               | B5              | B7                                  |  |

|                    |          |     |                 | PD[8]       | GF            | GPIOD[2] / KI[3] |                 | G0                                  |  |

| 127~123,           | DD[00.0] | 10  |                 | PD[9]       | GP            | GPIOD[3] / KO[3] |                 | G1                                  |  |

| 120~112,<br>108~99 | PD[23:0] | Ю   |                 | PD[10]      | GPIOE[5]      | G0               | G0              | G2                                  |  |

| .00 00             |          |     |                 | PD[11]      | GPIOE[6]      | G1               | G1              | G3                                  |  |

|                    |          |     |                 | PD[12]      | GPIOE[7]      | G2               | G2              | G4                                  |  |

|                    |          |     |                 | PD[13]      | GPIOF[0]      | G3               | G3              | G5                                  |  |

|                    |          |     |                 | PD[14]      | GPIOF[1]      | G4               | G4              | G6                                  |  |

|                    |          |     |                 | PD[15]      | GPIOF[2]      | G5               | G5              | G7                                  |  |

|                    |          |     |                 | PD[16]      | GP            | PIOD[4] / KC     | )[1]            | R0                                  |  |

|                    |          |     |                 | PD[17]      | GP            | IOD[5] / KO      | I[2]            | R1                                  |  |

|                    |          |     |                 | PD[18]      | GPIOD[7       | '] / KO[4]       | R0              | R2                                  |  |

|                    |          |     |                 | PD[19]      | GPIOF[3]      | R0               | R1              | R3                                  |  |

|                    |          |     |                 | PD[20]      | GPIOF[4]      | R1               | R2              | R4                                  |  |

|                    |          |     |                 | PD[21]      | GPIOF[5]      | R2               | R3              | R5                                  |  |

|                    |          |     |                 | PD[22]      | GPIOF[6]      | R3               | R4              | R6                                  |  |

|                    |          |     |                 | PD[23]      | GPIOF[7]      | R4               | R5              | R7                                  |  |

|                    |          |     | pins            | s. The Defa |               | of LCD I/F is    | s 18bpp fun     | and Key-Mati<br>ction mode, s       |  |

**Table A-6: LCD Driver Signals (Continued)**

| Pin# | Pin Name | I/O | Pin Description                                                                                   |

|------|----------|-----|---------------------------------------------------------------------------------------------------|

| 96   | PCLK     | 0   | Panel Scan Clock Generic TFT interface signal for panel scan clock. It derives from internal PLL. |

| 93   | VSYNC    | 0   | VSYNC Pulse Generic TFT interface signal for vertical synchronous pulse.                          |

| 94   | HSYNC    | 0   | HSYNC Pulse Generic TFT interface signal for horizontal synchronous pulse.                        |

| 95   | PDE      | 0   | Data Enable Generic TFT interface signal for data valid or data enable.                           |

# **PWM Output Signals (2 Pins)**

**Table A-7: PWM Output Signals**

| Pin# | Pin Name                     | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 90   | PWM[0] INITDIS GPIOC[7] CCLK | Ю   | PWM Output 0 / Initial Display Enable  PWM[0]: PWM"s output signal. The output mode is decided by configuration register. This pin can be used as the control signal of TFT panel"s back light.  INITDIS: Pull-high this pin will enable Initial Display function. This pin has internal pull-down in reset period to disable Initial Display function by default. i.e. after reset complete, internal pull-down resistor will be disabled.  If PWM function disabled then it can be programmed as GPIO C[7], and default is GPIOC[7] input function, or output Core Clock - CCLK. |

| 91   | PWM[1]                       | Ю   | PWM Output 1  PWM"s output signal. The output mode and output function is decided by configuration register. This pin also can be used as the control signal of TFT panel"s back light.  When TEST[0] set high, then PWM[1] pin is external panel scan clock input                                                                                                                                                                                                                                                                                                                 |

# **GPIO Signals** (28 Pins)

Table A-8: General Purpose I/O Signals

| Pin#                                        | Pin Name                          | I/O | Pin Description                                                                                                                                                                                                                                                                  |

|---------------------------------------------|-----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35~28                                       | GPIOA[7:0]                        | Ю   | GPIO A Group These are general purpose I/O. These are multiplex pins that share with DB[15:8]. They are available when 8bits parallel host mode and serial Host mode.                                                                                                            |

| 92,<br>128,<br>16~13                        | GPIB[4],<br>GPOB[4],<br>GPIB[3:0] | Ю   | GPIO B Group  These are general purpose I/O. GPIB[3:0] are read only and available in serial host mode.  GPIB[4] is same pin with KI[0].  GPOB[4] is same pin with KO[0].  GPIB[3:0] are multiplex pins that share with {A0, WR#, RD#, CS#}.                                     |

| 90, 38,<br>37,<br>41~39                     | GPIOC[7],<br>GPIOC[4:0]           | Ю   | GPIO C Group  These are general purpose I/O. GPIOC are available when PWM and SPI Master functions disabled.  GPIOC[7] is same pin with PWM[0].  GPIOC[4:0] are multiplex pins that share with {SFCS1#, SFCS0#, SFDI, SFDO, SFCLK}                                               |

| 120, 101<br>119, 118<br>108, 107<br>100, 99 | GPIOD[7:0]                        | Ю   | GPIO D Group  These are general purpose I/O.  GPIOD[7:0] are multiplex pins that share with PD[18, 2, 17, 16, 9, 8, 1, 0].  GPIOD[5,4,3,2,1,0] are available when LCD Panel interface is set 16bits or 18bits.  GPIOD[7,6] are available when LCD Panel interface is set 16bits. |

# **Key-Matrix Signals (10 Pins)**

Table A-9: Key-Matrix Signals

| Pin#                        | Pin Name | I/O | Pin Description                                                                                                                                                                                                                                                       |

|-----------------------------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 101, 107,<br>100, 99,<br>92 | KI[4:0]  | ı   | Key-Matrix Data Pins Keypad data inputs with internal pull-up resister. KI[4:1] are multiplex pins that share with PD[8] and PD[2:0]. The Key-matrix function will be disable when LCD I/F are set as 24bits. XKIN[0] also provide the I2CMCK function of I2C Master. |

| 120,108,<br>119,118,<br>128 | KO[4:0]  | 0   | Key-Matrix Strobe Pins Keypad strobe data outputs with Open-Drain. KO[4:1] are multiplex pins that share with PD[9] and PD[18:16]. KO[0] also provide the I2CMDA function of I2C Master.                                                                              |

# **Power and Clock Signals (23 Pins)**

**Table A-10: Power and Clock Signals**

| Pin#                                            | Pin Name | I/O | Pin Description                                                                                                                                                                                                                         |

|-------------------------------------------------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                               | XI       | I   | Crystal / External Clock Input  This input pin is used for internal crystal circuit or external clock that generate clock source for PLL. It should be connected to external crystal or clock, and suggested frequency is 8.0 ~ 12 MHz. |

| 2                                               | ХО       | 0   | Crystal Output  This is an output pin for internal crystal circuit. It should be connected to external crystal circuit.                                                                                                                 |

| 4, 63,<br>111                                   | VDD_C    | PWR | Internal LDO Output These pins must connect 1uF and 0.1uF capacitor to ground.                                                                                                                                                          |

| 3, 23,<br>42, 62,<br>75, 88,<br>97, 109,<br>121 | VDD      | PWR | 3.3V Power Pins                                                                                                                                                                                                                         |

| 5, 24,<br>43, 64,<br>76, 89<br>98, 110,<br>122  | VSS      | PWR | Ground(GND) Pins                                                                                                                                                                                                                        |

# **Reset and Test Signals (4 Pins)**

**Table A-11: Reset and Test Signals**

| Pin# | Pin Name  | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                             |

|------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12   | RST#      | I/O | Reset Signal Input  This is a active low Reset pin for LT768x. To avoid noise interfere and cause fake reset behavior, this pin is active at least 256 OSC clocks.                                                                                                                                                                                          |

| 6~8  | TEST[2:0] | I   | Test Input  These pins are used for testing and normally connect to GND.  If TEST[0] keep high, the internal PLL will be disable and the system clock is supply by external.  If TEST[2:1] keep 01b, then the SPI Master signals will keep floating. This feature allow external device to program Serial Flash directly. (i.e. ISP, In-System-Programming) |

# Pin Description -2 (LT7680x-R/68Pin-QFN)

LT7680 is a 68Pin QFN type package chip. The following tables are their pins function list. For detail pins description, please refer to the previous section - Pin Description -1.

### **Host Interface Select Signals (2 Pins)**

Table A-12: Host I/F Select Signals

| Pin# | Pin Name | I/O |         | Pin Description       |                 |  |  |

|------|----------|-----|---------|-----------------------|-----------------|--|--|

|      |          |     | Host Ir | nterface Selection    |                 |  |  |

|      | PSM[2]   | _   |         | PSM[2] PSM[0]         | Host I/F Mode   |  |  |

| 8~9  | PSM[0]   | I   |         | 1 0                   | 3-Wire SPI Mode |  |  |

|      |          |     |         | 1 1                   | 4-Wire SPI Mode |  |  |

|      |          |     | The PS  | SM[2] pin must connex | ct to Hi.       |  |  |

# **Host Serial I/F Signals (5 Pins)**

Table A-13: Host Serial I/F Signals

| Pin# | Pin Name | I/O | Pin Description         |

|------|----------|-----|-------------------------|

| 17   | SCLK     | I   | SPI Clock               |

| 16   | SDI      | I   | 4-wire SPI Data Input   |

|      | SD       |     | 3-wire SPI Data         |

| 15   | SDO      | Ю   | 4-wire SPI Data Output  |

| 11   | SCS#     | I   | SPI Chip Select         |

| 19   | INT#     | 0   | Interrupt Output Signal |

## **LCD Driver Signals (22 Pins)**

Table A-14: LCD Driver Signals

| Pin#                                     | Pin Name                             | I/O | Pin Description    |

|------------------------------------------|--------------------------------------|-----|--------------------|

| 2~1,<br>68~66,<br>64,<br>63~58,<br>56~51 | PD[23:18],<br>PD[15:10],<br>PD[7:2], | Ю   | LCD Panel Data Bus |

| 49                                       | PCLK                                 | 0   | Panel Scan Clock   |

| 46                                       | VSYNC                                | 0   | VSYNC Pulse        |

| 47                                       | HSYNC                                | 0   | HSYNC Pulse        |

| 48                                       | PDE                                  | 0   | Data Enable        |

LT768x DS ENG / V4.0

# **External Serial Flash / SPI Master Signals (5 Pins)**

**Table A-15: External Serial Flash Signals**

| Pin#  | Pin Name   | I/O | Pin Description                                       |

|-------|------------|-----|-------------------------------------------------------|

| 21~20 | SFCS[1:0]# | Ю   | Chip Select 0 for External Serial Flash or SPI device |

| 22    | SFCLK      | Ю   | SPI Serial Clock                                      |

| 23    | SFDO       | Ю   | Master Output Slave Input                             |

| 24    | SFDI       | Ю   | Master Input Slave Output                             |

# **PWM Output Signals (2 Pins)**

**Table A-16: PWM Output Signals**

|   | Pin# | Pin Name | I/O | Pin Description                       |  |

|---|------|----------|-----|---------------------------------------|--|

|   | 45   | PWM[0]   | Ю   | PWM Output 0 / Initial Display Enable |  |

| Ī | 44   | PWM[1]   | Ю   | PWM Output 1                          |  |

### **GPIO Signals (7 Pins)**

Table A-17: General Purpose I/O Signals

| Pin#    | Pin Name   | I/O | Pin Description |

|---------|------------|-----|-----------------|

| 18      | GPIOA[7]   | Ю   | GPIO A Group    |

| 44, 21, | GPIOC[7]   |     |                 |

| 20, 24, | GPIOC[4:0] | Ю   | GPIO C Group    |

| 23, 22  | GP10C[4.0] |     |                 |

### Reset (1 Pins)

Table A-18: Reset Signal

| Pin# | Pin Name | I/O | Pin Description    |

|------|----------|-----|--------------------|

| 10   | RST#     | I/O | Reset Signal Input |

# **Power and Clock Signals (26 Pins)**

Table A-19: Power and Clock Signals

| Pin#                                               | Pin Name    | I/O | Pin Description                                       |

|----------------------------------------------------|-------------|-----|-------------------------------------------------------|

| 3                                                  | XI          | I   | Crystal / External Clock Input                        |

| 4                                                  | ХО          | 0   | Crystal Output                                        |

| 6, 13,<br>27, 31,<br>40                            | VDD_C       | PWR | Internal LDO Output                                   |

| 5, 12,<br>25, 30,<br>39, 42,<br>50, 65             | VDD         | PWR | 3.3V Power Pins                                       |

| 7, 14,<br>26, 32,<br>34, 35,<br>37, 41,<br>43, 57, | VSS         | PWR | Ground(GND) Pins                                      |

|                                                    | Thermal Pad | -   | The back of LT7680 Heat sink pad must tied to ground. |

# Absolute Maximum Ratings

**Table A-20: Absolute Maximum Ratings**

| Symbol           | Parameter                   | Value          | Unit |

|------------------|-----------------------------|----------------|------|

| $V_{DD}$         | Supply Voltage Range        | -0.3 ~ 4.0     | V    |

| V <sub>IN</sub>  | Input Voltage Range         | -0.3 ~ VDD+0.3 | V    |

| V <sub>OUT</sub> | Output Voltage Range        | -0.3 ~ VDD+0.3 | V    |

| P <sub>D</sub>   | Power Dissipation           | <u>≤</u> 300   | mW   |

| T <sub>OPR</sub> | Operation Temperature Range | -45 ~ 85       | ℃    |

| T <sub>ST</sub>  | Storage Temperature         | -45 ~ 125      | ℃    |

| T <sub>SOL</sub> | Soldering Temperature       | 260            | ℃    |

#### Note:

If used beyond the absolute maximum ratings, LT768x may be permanently damaged. It is strongly recommended that the device be used within the electrical characteristics in normal operations. If exposed to the condition not within the electrical characteristics, it may affect the reliability of the device. This specification does not guarantee the accuracy of the parameters without a given upper and lower limit value, but it stypical value reasonably reflects the device performance.

# Electrical Characteristics (Condition: V<sub>DD</sub> = 3.3V, T<sub>A</sub> = 25 °C)

**Table A-21: Electrical Characteristics**

| Symbol              | Parameter                  | Condition                           | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------|-------------------------------------|------|------|------|------|

| $V_{DD}$            | System Voltage             |                                     | 3.0  | 3.3  | 3.6  | V    |

| $C_{VDD}$           | Loading Capacitor          |                                     | 1    | 1    | 10   | uF   |

| I <sub>OPR</sub>    | Operation Current          | Note 1                              |      | 60   |      | mA   |

| I <sub>STB</sub>    | Standby Mode               | Note 1                              |      | 30   |      | mA   |

| I <sub>SUSP</sub>   | Suspend Mode               | Note 1                              |      | 10   |      | mA   |

| I <sub>SLP</sub>    | Sleep Mode                 | Note 1                              |      | 7    |      | mA   |

| T <sub>RMP</sub>    | Power Ramp Up Time         | VDD Ramp<br>Up to 3.3 V             | 3.5  |      | 35   | ms   |

| OSC / PLL           |                            |                                     |      |      |      |      |

| F <sub>osc</sub>    | Oscillator Clock           | $V_{DD} = 3.3 \text{ V},$<br>Note 2 |      | 10   |      | MHz  |

| F <sub>VCO</sub>    | VCO Output Clock Frequency |                                     | 100  |      | 500  | MHz  |

| T <sub>LOCK</sub>   | Lock Time                  | Note 3                              |      |      | 500  | us   |

| CLK <sub>MPLL</sub> | MPLL Output Clock (MCLK)   | VDD = 3.3 V                         |      |      | 133  | MHz  |

| CLK <sub>CPLL</sub> | CPLL Output Clock (CCLK)   | VDD = 3.3 V                         |      |      | 100  | MHz  |

| CLK <sub>PPLL</sub> | PPLL Output Clock (PCLK)   | VDD = 3.3 V                         |      |      | 80   | MHz  |

**Table A-21: Electrical Characteristics (Continued)**

| Symbol                | Parameter                             | Condition         | Min.       | Тур.    | Max. | Unit |  |  |

|-----------------------|---------------------------------------|-------------------|------------|---------|------|------|--|--|

| Serial Host Interface |                                       |                   |            |         |      |      |  |  |

| CLK <sub>SPI</sub>    | SPI Input Clock                       |                   |            |         | 50   | MHz  |  |  |

| Input/Output (CMC     | OS 3-state Output pad with Schm       | nitt Trigger Inpu | ıt, Pull-U | Jp/Down | )    |      |  |  |

| V <sub>IH</sub>       | Input High Voltage                    |                   | 2          |         | 3.6  | V    |  |  |

| V <sub>IL</sub>       | Input Low Voltage                     |                   | -0.3       |         | 8.0  | V    |  |  |

| V <sub>OH</sub>       | Output High Voltage                   |                   | 2.4        |         |      | V    |  |  |

| V <sub>OL</sub>       | Output Low Voltage                    |                   |            |         | 0.4  | V    |  |  |

| $R_{PU}$              | Pull up Resistance                    |                   | 34         | 41      | 64   | ΚΩ   |  |  |

| R <sub>PD</sub>       | Pull down Resistance                  |                   | 33         | 44      | 79   | ΚΩ   |  |  |

| V <sub>TP</sub>       | Schmitt Trigger Low to High Threshold |                   | 1.5        |         | 2.1  | V    |  |  |

| V <sub>TN</sub>       | Schmitt Trigger High to Low Threshold |                   | 0.8        |         | 1.3  | V    |  |  |

| V <sub>HVS</sub>      | Hysteresis Voltage                    |                   | 200        |         |      | mV   |  |  |

| I <sub>LEAK</sub>     | Input Leakage Current                 |                   | -10        |         | +10  | μΑ   |  |  |

| $V_{SLEW}$            | Rise/Fall Slew Rate                   |                   |            | 1.5     |      | V/ns |  |  |

Note 1: Measured on tester with 8 bit MPU interface and without extra load.

Note 2: Parasitic effect used in the Crystal Oscillator.

Typical: R1 =  $50\Omega$  (25- $100\Omega$ ), L1 = 3.4mH, C1 = 13fF, C0 = 2.8pF

Figure A-6: Equivalent Circuit

Note 3: Time from power-up or change PLLs" parameters until to PLL have stable clock output.

# Function Description

#### 1. Clock and Reset

#### 1.1 Clock

LT768x embedded three PLL circuit to generate three clock source for internal circuit operation:

■ CPLL : Provide **CCLK** for Host interface, BTE Engine, Graphics Engine, and Text DMA data transfer etc...

MPLL : Provide MCLK for internal Display RAM

PPLL : Provide PCLK for TFT-LCD"s Scan Clock.

The three PLL are operation independent. The PLL output frequency is calculated from the following formula:

$$F_{OUT} = XI * (N / R) \div OD$$

In above formula, XI is the external Oscillator / Clock input. The input frequency "XIN/R" is no less than 1MHz, and the default value is 1MHz. "R" is Input Divider Ratio, it between  $2 \sim 31$ . "OD" is Output Divider Ratio that must be 1, 2 or 4. "N" is the Feedback Divider Ratio of Loop that indicated by 9bits which between  $2 \sim 511$ .

Input Divider Feedback Divider R[4:0] N[8:0] Ratio (R) Ratio (N) 00010 2 00000010 2 00011 3 00000011 3 00101 4 000000101 4 11101 29 111111101 509 11110 30 111111110 510 11111 31 111111111 511

Table 1-1: PLL Register Setting (1)

Table 1-2: PLL Register Setting (2)

| OD[1:0] | Input Divider Ratio (OD) |

|---------|--------------------------|

| 00      | 1                        |

| 01      | 2                        |

| 10      | 3                        |

| 11      | 4                        |

LT768x DS ENG / V4.0

For example, XI is 10MHz, R[4:0] is 01010 (i.e. 10), N[8:0] is 100000000 (i.e. 256), OD[1:0] is 11 (i.e. 4), then:

$$F_{OUT} = 10MHz * (256 / 10) \div 4 = 64MHz$$

The design rule of three clock are::

- 1. CCLK\*2 >= MCLK >= CCLK

- 2. CCLK >= PCLK \* 1.5

Usually TFT manufacturers will be based on their TFT characteristics to inform the best display of Pixel Clock (PCLK). Therefore, user can setup the register according to the requirements of the PCLK. And according to the above rule to setup CCLK and MCLK.

According to the different resolution of LCD panel, the PLL output should generate different clock frequency. For example, if LCD panel resolution is 640\*480, the recommend values are: PCLK = 20MHz, MCLK = 40MHz, CCLK = 40MHz, then the register are setting as following:

Another example, if resolution is 800\*480, the recommend values are: PCLK = 25MHz, MCLK = 50MHz, CCLK = 50MHz. We can setup the registers" values as following:

Table 1-3: PLL Register Setting Example

| Registers        | 640*480   | 800*480   |

|------------------|-----------|-----------|

| REG[05h], PPLLC1 | 11010100b | 11010100b |

| REG[06h], PPLLC2 | 01010000b | 01100100b |

| REG[07h], MPLLC1 | 11010100b | 11010100b |

| REG[08h], MPLLC2 | 10100000b | 11001000b |

| REG[09h], CPLLC1 | 11010100b | 11010100b |

| REG[0Ah], CPLLC1 | 10100000b | 11001000b |

#### 1.2 Reset

#### 1.2.1 Power-on Reset

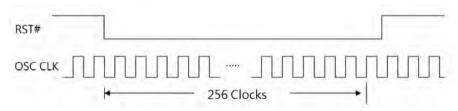

LT768x embedded a Power-On-Reset for core system. It is an active low signal and may output to external circuits by RST# pin to synchronize whole system. When system power (3.3V) on, internal reset will active until internal power stable and then de-active after 256 OSC(X\*tal Oscillator) clocks.

#### 1.2.2 External Reset

LT768x has capability to receive external reset(RST#) event to synchronize with external system. The external reset event will be admitted when RST# keep low and stable at least 256 OSC clocks.

Before the start to access LT768x, Host should check it s Status Register(STSR) bit [1], i.e. operation mode status bit, and make sure it in Normal operation state.

Figure 1-1: External Reset Signal

### 1.2.3 Software Reset

If the Host write registers REG[00h] bit0 to 1, the LT768 will be reset by software. The software reset will only reset the internal state machine of LT768, and the other registers values will not be affected or cleared. After the software reset is complete, the REG[00h] bit0 will automatically be cleared to 0.

### 2. Host Interface

LT768x is control by external Host and through the host interface to access LT768x"s Registers and Display Memory. LT768x provide 8bits or 16bits parallel mode, serial SPI mode, and I2C mode for Host's communication. These interface mode is setup by PSM[2:0] pins:

PSM[2:0] Host Interface

0 0 X 8bits or 16bits 8080 Parallel Interface Mode

0 1 X 8bits or 16bits 6800 Parallel Interface Mode

1 0 0 3-Wire SPI Mode

1 0 1 4-Wire SPI Mode

1 1 X I2C Mode

Table 2-1: Host Interface Mode

Because the different MCU interfaces cannot be used at the same time, so LT768x provides a shared pin mode. When use Serial Mode, the other parallel pins can also be set to GPIO use. Please refer to the following table:

| Pin      |         |          | SPI           | SPI     | I2C        |            |            |         |            |    |     |         |

|----------|---------|----------|---------------|---------|------------|------------|------------|---------|------------|----|-----|---------|

| Name     | 8-bits  | 16-bits  | 8-bits        | 16-bits | 3-Wires    | 4-Wires    | 120        |         |            |    |     |         |

| DB[15:8] |         |          |               |         | GPIOA[0:7] | GPIOA[0:7] | GPIOA[0:7] |         |            |    |     |         |

| DB[7]    |         |          |               |         | SCLK       | SCLK       | SCLK       |         |            |    |     |         |

| DB[6]    |         | DD[4E:0] | 5.01 DD[45.01 |         | GND        | SDI        | I2C_SDA    |         |            |    |     |         |

| DB[5]    | DB[7:0] | DB[15:0] | DB[7:0]       | DB[7:0] | DB[7:0]    | DB[7:0]    | DB[7:0]    | DB[7:0] | DB[15:0] - | SD | SDO | I2CA[5] |

| DB[4]    |         |          |               |         |            |            | SCS#       | SCS#    | I2CA[4]    |    |     |         |

| DB[3:0]  |         |          |               |         | GND        | GND        | I2CA[3:0]  |         |            |    |     |         |

| CS#      | C       | S#       | C             | S#      | GPIB[0]    | GPIB[0]    | GPIB[0]    |         |            |    |     |         |

| RD#      | R       | D#       | Е             | EN      | GPIB[1]    | GPIB[1]    | GPIB[1]    |         |            |    |     |         |

| WR#      | W       | /R#      | R# RW#        |         | GPIB[2]    | GPIB[2]    | GPIB[2]    |         |            |    |     |         |

| A0       | A0      |          | A0            |         | GPIB[3]    | GPIB[3]    | GPIB[3]    |         |            |    |     |         |

| INT#     | IN      | IT#      | IN            | IT#     | INT#       | INT#       | INT#       |         |            |    |     |         |

| WAIT#    | W       | AIT#     | W             | AIT#    |            |            |            |         |            |    |     |         |

Table 2-2: The Pin Definition of Host Interface

When using the Parallel Host mode, 8bits or 16bits data transfer is determined by the bit0 of Register REG[01h]. When this bit0=0, then 8bits data transfer was selected. And if this bit0=1 then 16bits selected.

The LT768x series support different Host interfaces. For example, LT7680 is a 68pin QFN chip, which only supports serial SPI mode. The following table is Host interface supporting list for LT768x series:

Table 2-3: Host Interface Supporting List of LT768x Series

| No. | Host Interface Mode                 | LT7681<br>LT7683+<br>LT7686 | LT7680A-R<br>LT7680B-R |

|-----|-------------------------------------|-----------------------------|------------------------|

| 1   | 8bits 8080 Parallel Interface Mode  | ٧                           |                        |

| 2   | 16bits 8080 Parallel Interface Mode | ٧                           |                        |

| 3   | 8bits 6800 Parallel Interface Mode  | ٧                           |                        |

| 4   | 16bits 6800 Parallel Interface Mode | ٧                           |                        |

| 5   | 3-Wire SPI Mode                     | ٧                           | ٧                      |

| 6   | 4-Wire SPI Mode                     | ٧                           | ٧                      |

| 7   | I2C Mode                            | V                           |                        |

The Host interface is selected by pins PSM[2:0] except the LT7680. Please refer to previous Table 2-1. But LT7680 only supports 3-Wires and 4-Wires SPI mode. The PSM[1] pin already connected to GND within the LT7680, while PSM[2] must pull-up to VDD. When PSM[0] = 0, then the 3-wires SPI mode was selected. When PSM[0] = 1, serial 4-wires SPI mode was selected.

#### 2.1 Parallel Host Interface

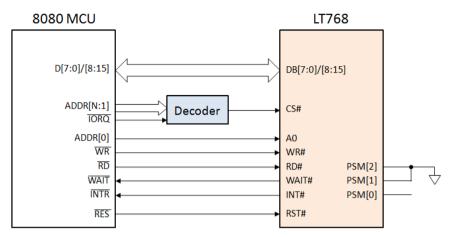

The following are the application circuit and timing of 8080/6800 parallel interface:

Figure 2-1: 8080 Parallel Mode Interface

The WAIT# signal is used to indicate LT768x is ready to transfer data or not. If WAIT# signal did not connect, then the Host access cycle time has to length than five CCLK clocks to avoid access fail. If the Host"s Reset signal is active low, then it can connect to RST# of LT768x. Of course, the RST# can also control by the I/O pin of host, or connect a RC circuit to generate a low pulse. However, either way to confirm RST#'s active cycle has to keep at least 256 system clock cycle. While using LT768x, Host should first confirm the state register bit1, to know whether the LT768x in the standard operating state.

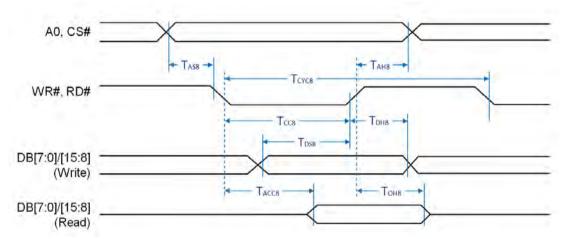

Figure 2-2: 8080 Parallel Mode Interface Timing

| Symbol            | Parameter               | Rating |      | Unit  | Note                           |  |

|-------------------|-------------------------|--------|------|-------|--------------------------------|--|

| Syllibol          | Parameter               | Min.   | Max. | Offic | Note                           |  |

| T <sub>CYC8</sub> | Cycle Time              | 50     |      | ns    |                                |  |

| T <sub>CC8</sub>  | Strobe Pulse Width      | 20     |      | ns    |                                |  |

| T <sub>AS8</sub>  | Address Setup Time      | 0      |      | ns    |                                |  |

| T <sub>AH8</sub>  | Address Hold Time       | 10     |      | ns    | tc is one system clock period: |  |

| T <sub>DS8</sub>  | Data Setup Time         | 20     |      | ns    | tc = 1/SYS_CLK                 |  |

| T <sub>DH8</sub>  | Data Hold Time          | 10     |      | ns    |                                |  |

| T <sub>ACC8</sub> | Data Output Access Time | 0      | 20   | ns    |                                |  |

| T <sub>OH8</sub>  | Data Output Hold Time   | 0      | 20   | ns    |                                |  |

Table 2-4: 8080 Parallel Mode Interface Timing Parameter

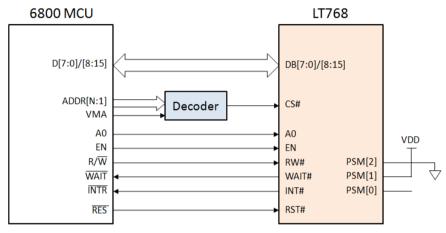

Figure 2-3: 6800 Parallel Mode Interface

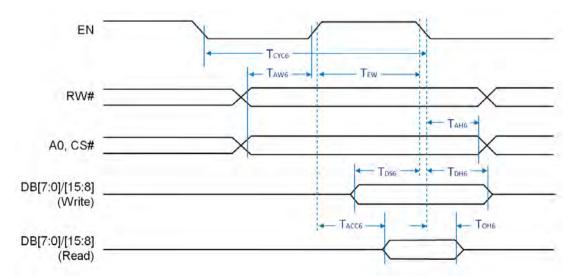

Figure 2-4: 6800 Parallel Mode Interface Timing

| Symbol            | Parameter               | Ra   | ting | Unit  | Note                           |  |

|-------------------|-------------------------|------|------|-------|--------------------------------|--|

| Syllibol          | r ai ailletei           | Min. | Max. | Oilit | Note                           |  |

| T <sub>CYC6</sub> | Cycle Time              | 50   |      | ns    |                                |  |

| $T_{EW}$          | Strobe Pulse Width      | 20   |      | ns    |                                |  |

| T <sub>AW6</sub>  | Address Setup Time      | 0    |      | ns    |                                |  |

| T <sub>AH6</sub>  | Address Hold Time       | 10   |      | ns    | tc is one system clock period: |  |

| T <sub>DS6</sub>  | Data Setup Time         | 20   |      | ns    | tc = 1/SYS_CLK                 |  |

| T <sub>DH6</sub>  | Data Hold Time          | 10   |      | ns    |                                |  |

| T <sub>ACC6</sub> | Data Output Access Time | 0    | 20   | ns    |                                |  |

| T <sub>OH6</sub>  | Data Output Hold Time   | 0    | 20   | ns    |                                |  |

Table 2-5: 6800 Parallel Mode Interface Timing Parameter

Host through the host interface to access LT768x"s Registers and Display Memory. LT768x has one Status Register and 256 Instruction Registers (i.e. .REG[00h] ~ REG[FF]). The access procedure are as following:

#### **Register Write:**

- 1. Address Write: Write the Register"s Address. For example, 00h i.e. REG[00h], 01h i.e. REG[01h], 02h i.e. REG[02h] .....

- 2. Data Write: Write Data to the Register

#### **Register Read:**

- 1. Address Write: Write the Register"s Address

- 2. Data Write: Read Data from the Register

Displays Memory (Display RAM) is where the TFT screen image data is stored,. Host through interface and write data into Display RAM. The procedure of access Display RAM is as following:

### **Display RAM Write:**

- 1. Set the Active Window Registers before writing any image data.

- 2. Perform an register write to Graphic R/W Position Register 0, REG[5Fh]).

- 3. Repeat step 2 until setup all the Active Window & Graphic R/W Position Coordinates.

- 4. Perform an address write to point to Memory Data Port Register (REG[04h])

- 5. Perform data writes to fill the window. Each write to the Memory Data Port will auto-increment the internal memory address.

#### 2.2 Serial Host Interface

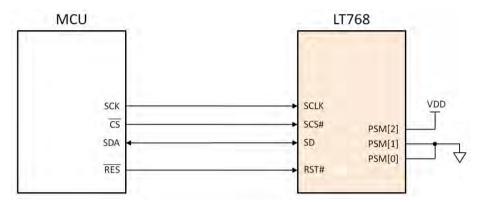

Figure 2-5: 3-Wire SPI Interface

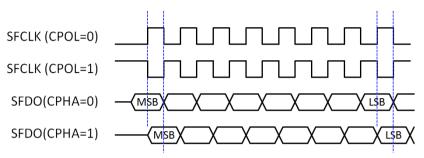

The above circuit is the LT768x"s 3-Wires SPI interface with Host. SD signal is a bi-direction data pin for data access. The access timing and procedure are as below:

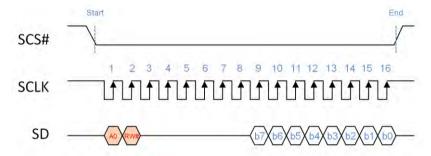

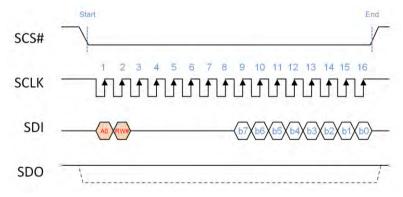

Figure 2-6: 3-Wire SPI Interface Timing

#### **Status Register Read:**

- 1. Host drive SCS#(Low) and SCLK(SPI Clock).

- 2. Host drive A0(Low), then drive RW#(High).

- 3. LT768x will drive the Data of Status Register (b7  $\sim$  b0) at 9<sup>th</sup>  $\sim$  16<sup>th</sup> Clock. Then Host will get the content of Status Register.

### Write Register's Address:

- 1. Host drive SCS#(Low) and SCLK.

- 2. Host drive A0(Low), then drive RW#(Low).

- 3. Host drive the Register"s Address (b0  $\sim$  b7) at 9<sup>th</sup>  $\sim$  16<sup>th</sup> Clock to LT768x.

#### Write Data to Register or Memory:

- 1. Host drive SCS#(Low) and SCLK.

- 2. Host drive A0(High), then drive RW#(Low).

- 3. Host drive the Data at  $9^{th} \sim 16^{th}$  Clock to LT768x. i.e. Data will be stored in Register or Memory.

LT768x DS ENG / V4.0

#### Read Register's Data:

- 1. Host drive SCS#(Low) and SCLK.

- 2. Host drive A0(High), then drive RW#(High).

- LT768x will drive the Data of Register at 9<sup>th</sup> ~ 16<sup>th</sup> Clock. Then Host will get the content of Register.

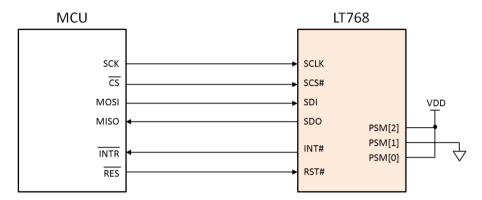

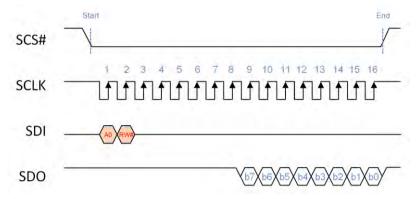

The 4-Wires SPI is almost same as 3-Wires. The difference is its data line input and output are separate. The interface circuit diagram and Timing are as follows:

Figure 2-7: 4-Wire SPI Interface

Figure 2-8: 4-Wire SPI Interface Write Timing

The above Timing diagram is the Write Cycle of 4-Wires SPI. When Host drive A0(Low) and RW#(Low), that see means Host write Register's Address. When Host drive A0(High), then RW#(Low) that seems Host write data to Register or Display RAM.

The following Timing diagram is the Read Cycle of 4-Wires SPI. When Host drive A0(Low) and RW#(High), that s means Host want to read the data of Status Register. LT768x will drive the Data of Status Register (b7  $\sim$  b0) at 9<sup>th</sup>  $\sim$  16<sup>th</sup> Clock. Then Host will get the data of Status Register. When Host drive A0(High), then RW#(High) that s means Host want to read the data of Command Register. LT768x will drive the Data of Command Register (b7  $\sim$  b0) at 9<sup>th</sup>  $\sim$  16<sup>th</sup> Clock for Host. Of course, Host will get the content of Command Register.

Figure 2-9: 4-Wire SPI Interface Read Timing

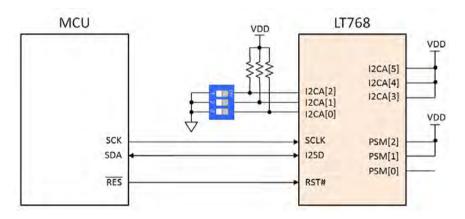

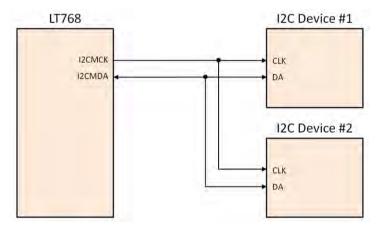

The serial I2C interface is also almost same as 3-Wires SPI interface. But I2C interface only need 2 wires for data transfer. The following is the application circuit of I2C interface. Signals I2CA[5:0] are used to setup LT768x"s Device ID, and to avoid confuse with other"s I2C device. In this example circuit, I2CA[5:3] connect to VDD, and if all DIP Switch are "ON" state, then I2C Device ID is 111000b. i.e. 38h. Therefore if Host drive I2C timing with "111000b" Device ID, then LT768x will communicate in the I2C cycle time with Host.

Figure 2-10: I2C Interface

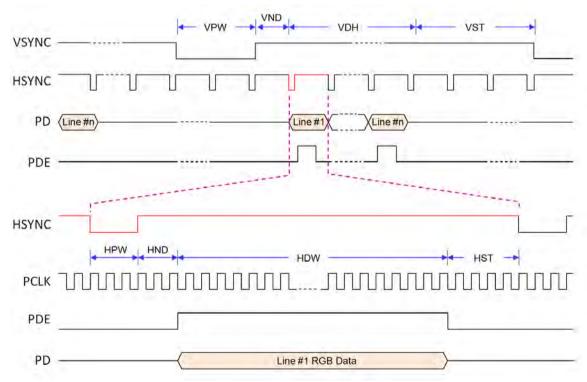

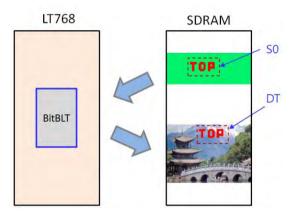

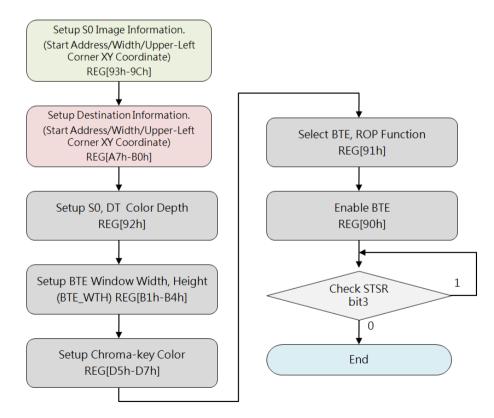

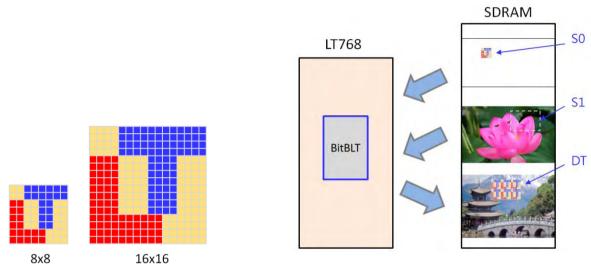

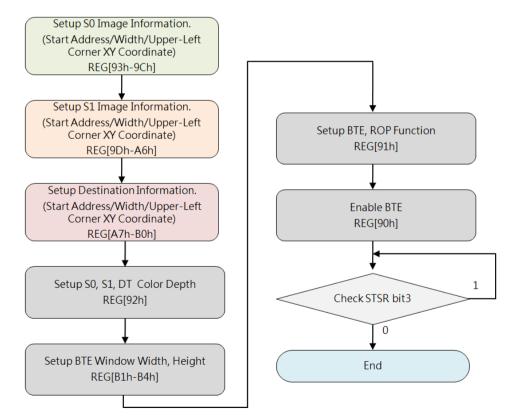

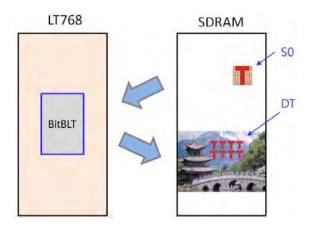

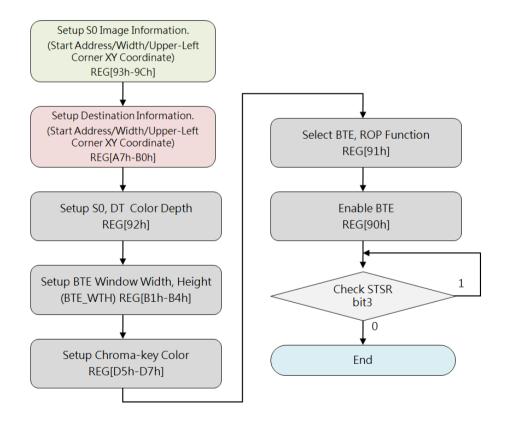

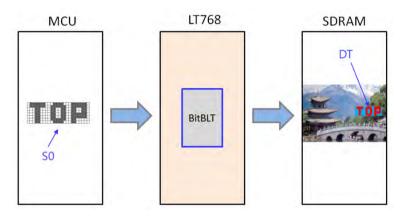

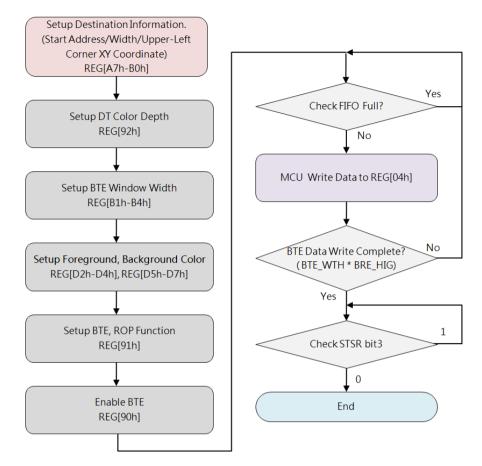

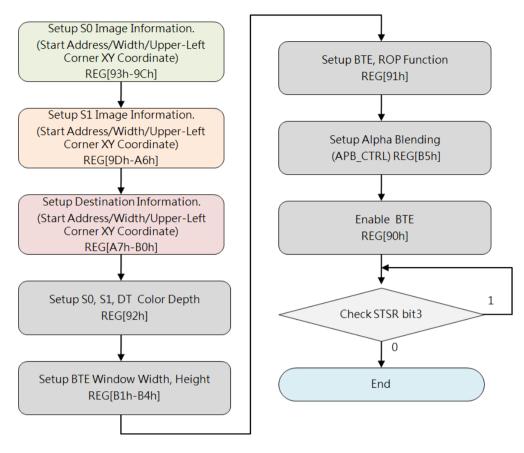

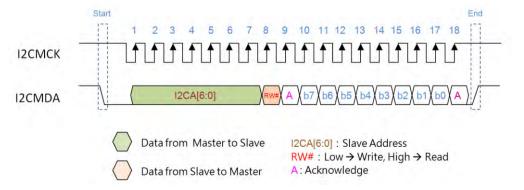

Figure 2-11: I2C Interface Timing