# **US2066**

# 100 x 32 OLED/PLED Segment/Common Driver with Controller For 20x4 Characters

### 1 General Description

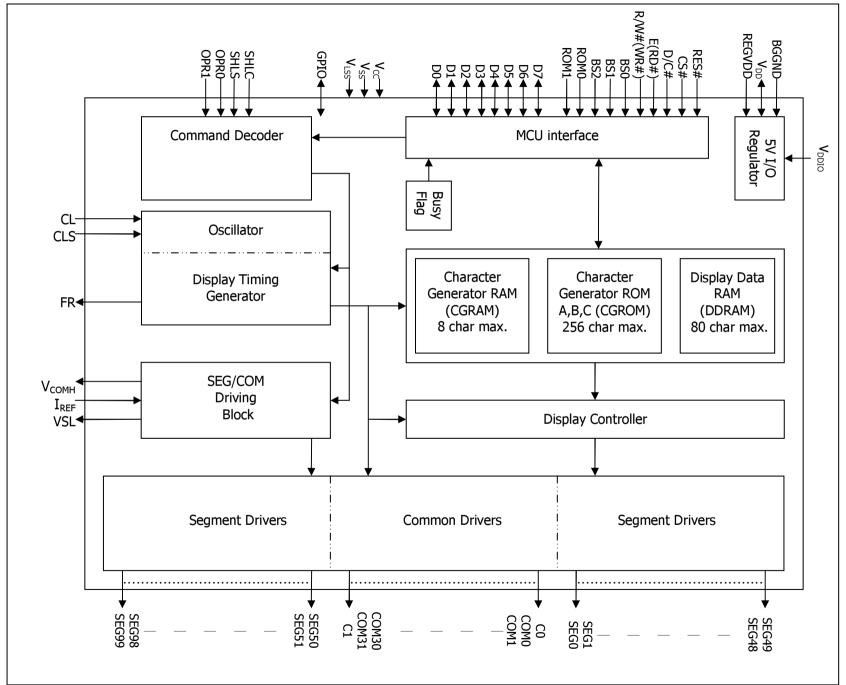

US2066 is a single-chip CMOS OLED/PLED driver with controller for organic/polymer light emitting diode dot-matrix graphic display. It consists of 100 segments and 34 commons while it can display 1, 2, 3, or 4 lines with 5x8 or 6x8 dots format. This IC is designed for Common Cathode type OLED/PLED panel.

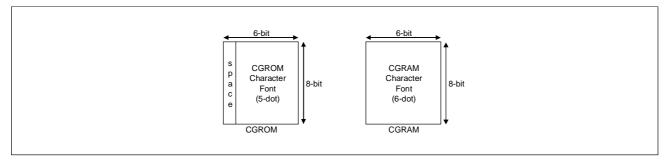

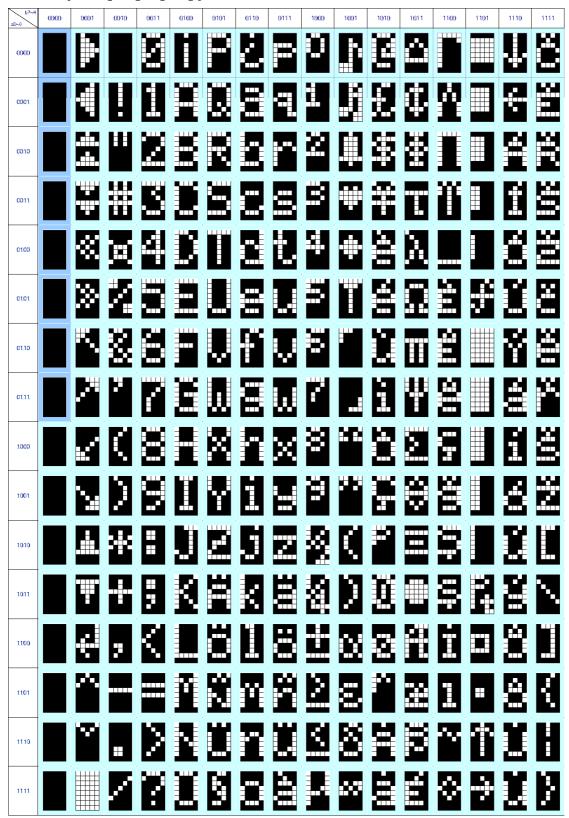

US2066 displays character directly from its internal 10,240 bits (256 characters x 5 x 8 dots) Character Generator ROM (CGROM). All the character codes are stored in the 640 bits (80 characters) Data Display RAM (DDRAM). User defined character can be loaded via 512 bits (8 characters) Character Generator RAM (CGRAM). Data/Commands are sent from general MCU through software selectable 4-/8-bit 68XX/80XX series compatible Parallel Interface,  $I^2C$  interface or Serial Peripheral Interfaces.

The contrast control and oscillator which embedded in US2066 reduce the number of external components. With the special design on minimizing power consumption, US2066 is suitable for portable applications requiring a compact size.

### 2 Features

- Resolution: 100 x 32 dot matrix panel

- Power supply (2 options selected by hardware configuration):

[Low voltage I/O application]

- V<sub>DDIO</sub> = 2.4V to 3.6V (MCU interface logic level)

- o  $V_{DD} = 2.4V$  to  $V_{DDIO}$ (Low voltage power supply)

- V<sub>CC</sub> = 8.0V to 15.0V (Panel driving power supply)

### [5V I/O application]

- $\circ \qquad V_{\text{DDIO}} = 4.4 \text{V to } 5.5 \text{V}$  (MCU interface logic level)

- V<sub>DD</sub> is internally regulated, a stabilizing capacitor is needed

- V<sub>CC</sub> = 8.0V to 15.0V (Panel driving power supply)

- Segment maximum source current: 450uA

- Common maximum sink current: 45mA

- 256-step Contrast Control

- Pin selectable MCU Interfaces:

- o 4 / 8-bit 6800/8080-series parallel interface

- Serial Peripheral Interface

- I<sup>2</sup>C Interface (Up to 400kbit/s)

- On-Chip Memories

- Character Generator ROM (CGROM):

10,240 bits (256 characters x 5 x 8 dot)

- Character Generator RAM (CGRAM):

64 x 8 bits (8 characters)

- Display Data RAM (DDRAM):80 x 8 bits (80 characters max.)

- Selectable duty cycle: 1/8, 1/16, 1/24, 1/32

- 1, 2, 3 or 4 lines with 5x8 or 6x8 dots format display

- 3 sets of CGROM (ROM A / B / C hardware pin selectable)

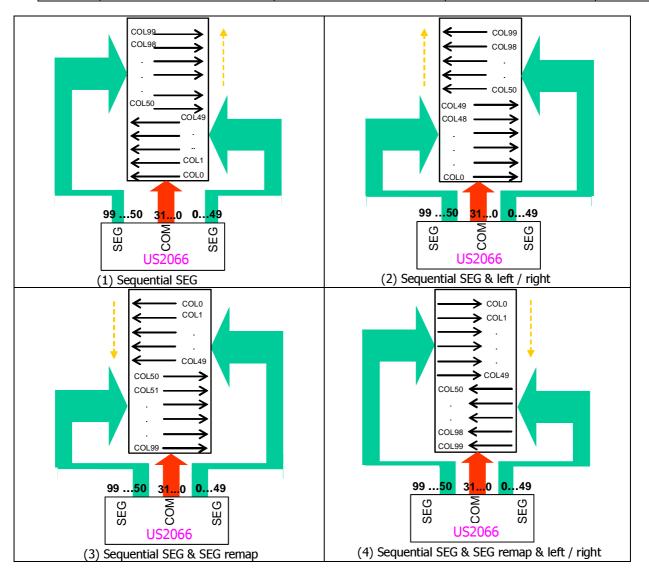

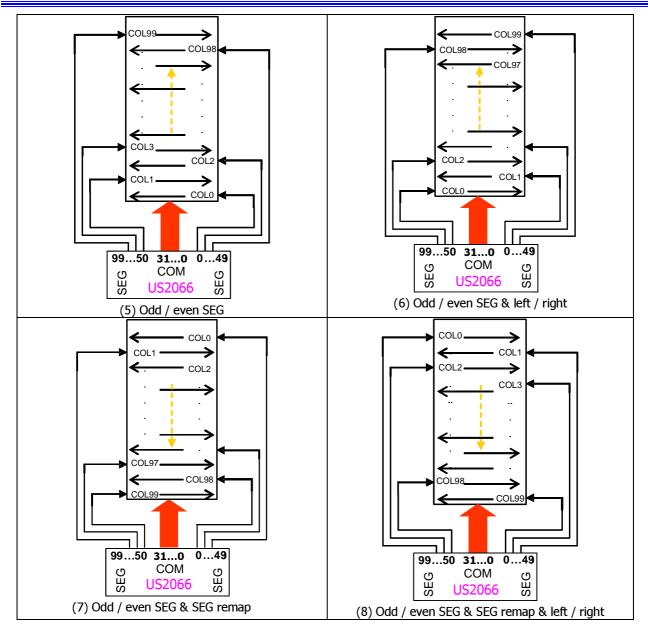

- Row Re-mapping and Column Re-mapping

- Double-height Font characters

- · Bi-direction shift function

- All character reverse display

- · Display shift per line

- Automatic power on reset

- Screen saving continuous scrolling function in horizontal direction (character by character)

- Screen saving fade in / out feature

- Programmable Frame Frequency

- Smart Cross-talk compensation scheme

- On-Chip Oscillator

- Chip layout for COG

- Wide range of operating temperatures: -40°C to 85°C

### 2.1 5-dot / 6-dot font width

Table 2-1: 5-dot / 6-dot font width

| Table 2-1: 5-dot / 6-dot font width |            |                          |                          |  |  |  |

|-------------------------------------|------------|--------------------------|--------------------------|--|--|--|

| Display Line                        | Duty Ratio | 5-dot font width         | 6-dot font width         |  |  |  |

| Numbers                             | Duty Ratio | Displayable Characters   | Displayable Characters   |  |  |  |

| 1                                   | 1/8        | 1 lines of 20 characters | 1 lines of 16 characters |  |  |  |

| 2                                   | 1/16       | 2 lines of 20 characters | 2 lines of 16 characters |  |  |  |

| 3                                   | 1/24       | 3 lines of 20 characters | 3 lines of 16 characters |  |  |  |

| 4                                   | 1/32       | 4 lines of 20 characters | 4 lines of 16 characters |  |  |  |

# Block Diagram

Figure 3-1: US2066 Block Diagram

3

# 4 Pin Descriptions

### Key:

| I = Input                           | NC = Not Connected                      |

|-------------------------------------|-----------------------------------------|

| O =Output                           | Pull LOW= connect to Ground             |

| I/O = Bi-directional (input/output) | Pull HIGH= connect to V <sub>DDIO</sub> |

| P = Power pin                       |                                         |

Table 4-1: US2066 Pin Description

| Pin Name          | Pin Type | Description                                                                                                                                                                                                        |  |  |  |  |  |  |

|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| V <sub>DD</sub>   | Р        | Power supply for core logic operation.                                                                                                                                                                             |  |  |  |  |  |  |

|                   |          | V <sub>DD</sub> can be supplied externally or regulated internally.                                                                                                                                                |  |  |  |  |  |  |

|                   |          | In LV IO application (internal $V_{DD}$ is disabled), this is a power input pin.                                                                                                                                   |  |  |  |  |  |  |

|                   |          | In 5V IO application (internal $V_{DD}$ is enabled), $V_{DD}$ is regulated internally from $V_{DDIO}$ .                                                                                                            |  |  |  |  |  |  |

|                   |          | A capacitor should be connected between $V_{\text{DD}}$ and $V_{\text{SS}}$ under all circumstances.                                                                                                               |  |  |  |  |  |  |

| V <sub>DDIO</sub> | Р        | Low voltage power supply and power supply for interface logic level in both Low Voltage I/O and 5V I/O application. It should match with the MCU interface voltage level and must be connected to external source. |  |  |  |  |  |  |

| V <sub>CC</sub>   | Р        | Power supply for panel driving voltage. This is also the most positive power voltage supply                                                                                                                        |  |  |  |  |  |  |

|                   |          | pin. It is supplied by external high voltage source.                                                                                                                                                               |  |  |  |  |  |  |

| V <sub>SS</sub>   | Р        | Ground pin. It must be connected to external ground.                                                                                                                                                               |  |  |  |  |  |  |

| V <sub>LSS</sub>  | Р        | Analog system ground pin. It must be connected to external ground.                                                                                                                                                 |  |  |  |  |  |  |

| V <sub>COMH</sub> | P        | COM signal deselected voltage level.                                                                                                                                                                               |  |  |  |  |  |  |

| COMH              | '        | A capacitor should be connected between this pin and V <sub>SS</sub> .                                                                                                                                             |  |  |  |  |  |  |

|                   |          | No external power supply is allowed to connect to this pin.                                                                                                                                                        |  |  |  |  |  |  |

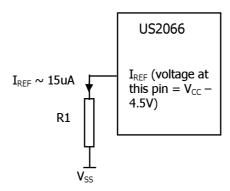

| $ m I_{REF}$      | I        | This pin is the segment output current reference pin.                                                                                                                                                              |  |  |  |  |  |  |

|                   |          | $I_{\text{REF}}$ is supplied externally. A resistor should be connected between this pin and $V_{\text{SS}}$ to maintain current of around 15uA.                                                                   |  |  |  |  |  |  |

| BS[2:0]           | I        | MCU bus interface selection pins. Select appropriate logic setting as described in the following table. BS2, BS1 and BS0 are pin select.                                                                           |  |  |  |  |  |  |

|                   |          | Table 4-2 : Bus Interface selection                                                                                                                                                                                |  |  |  |  |  |  |

|                   |          | BS[2:0] Interface                                                                                                                                                                                                  |  |  |  |  |  |  |

|                   |          | 000 Serial Interface                                                                                                                                                                                               |  |  |  |  |  |  |

|                   |          | 001 Invalid                                                                                                                                                                                                        |  |  |  |  |  |  |

|                   |          | $I^2C$                                                                                                                                                                                                             |  |  |  |  |  |  |

|                   |          | 011 Invalid                                                                                                                                                                                                        |  |  |  |  |  |  |

|                   |          | 100 8-bit 6800 parallel                                                                                                                                                                                            |  |  |  |  |  |  |

|                   |          | 101 4-bit 6800 parallel                                                                                                                                                                                            |  |  |  |  |  |  |

|                   |          | 110 8-bit 8080 parallel                                                                                                                                                                                            |  |  |  |  |  |  |

|                   |          | 111 4-bit 8080 parallel                                                                                                                                                                                            |  |  |  |  |  |  |

|                   |          | Note                                                                                                                                                                                                               |  |  |  |  |  |  |

|                   |          | $^{(1)}$ 0 is connected to $V_{SS}$ $^{(2)}$ 1 is connected to $V_{DDIO}$                                                                                                                                          |  |  |  |  |  |  |

|                   |          | I is connected to ADDIO                                                                                                                                                                                            |  |  |  |  |  |  |

|                   |          |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                   |          |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                   |          |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                   |          |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                   |          |                                                                                                                                                                                                                    |  |  |  |  |  |  |

| ·                 |          |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|          |   | 1                                               |                                                                                                                                                                                                              |                                         |             |                                               |                                |

|----------|---|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------|-----------------------------------------------|--------------------------------|

| Pin Name |   | Description                                     |                                                                                                                                                                                                              |                                         |             |                                               |                                |

| BGGND    | P | Reserved pin. It should be connected to ground. |                                                                                                                                                                                                              |                                         |             |                                               |                                |

| REGVDD   | I | Internal V <sub>DD</sub> regula                 | tor selection                                                                                                                                                                                                | on pin in 5V                            | ' I/O appl  | ication mode.                                 |                                |

|          |   |                                                 | When this pin is pulled HIGH, internal $V_{\text{DD}}$ regulator is enabled (5V I/O application). When this pin is pulled LOW, internal $V_{\text{DD}}$ regulator is disabled (Low voltage I/O application). |                                         |             |                                               |                                |

|          |   |                                                 |                                                                                                                                                                                                              |                                         |             | egulator can also be aving; details refer to  | disabled by extended           |

| SHLC     | I | This pin is used to                             | determine                                                                                                                                                                                                    | the Comm                                | on output   | scanning direction.                           |                                |

|          |   | Table 4-3 : COM                                 | scan dire                                                                                                                                                                                                    | ction                                   |             |                                               |                                |

|          |   |                                                 | SHL                                                                                                                                                                                                          | C COI                                   | 1 scan dir  | ection                                        |                                |

|          |   |                                                 | 1                                                                                                                                                                                                            | COI                                     | 10 to COI   | 431 (Normal)                                  |                                |

|          |   |                                                 | 0                                                                                                                                                                                                            | COI                                     | 431 to CC   | OMO (Reverse)                                 |                                |

|          |   | Note (1) 0 is connected to                      | o V.                                                                                                                                                                                                         |                                         |             |                                               |                                |

|          |   | (2) 1 is connected to                           |                                                                                                                                                                                                              |                                         |             |                                               |                                |

| SHLS     | I | This pip is used to                             | change t                                                                                                                                                                                                     | he mannin                               | n hetwee    | n the display data col                        | umn address and the            |

| SILS     | 1 | Segment driver. R                               |                                                                                                                                                                                                              |                                         |             | n the display data col                        | unin address and the           |

|          |   |                                                 | ordr to run                                                                                                                                                                                                  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | actano.     |                                               |                                |

|          |   | Table 4-4 : SEG s                               | can direc                                                                                                                                                                                                    | tion                                    |             |                                               |                                |

|          |   | Tuble 4 4 1 SEG S                               |                                                                                                                                                                                                              |                                         |             |                                               |                                |

|          |   |                                                 |                                                                                                                                                                                                              |                                         | G direction |                                               |                                |

|          |   |                                                 | 1                                                                                                                                                                                                            |                                         |             | G99 (Normal)                                  |                                |

|          |   | Note                                            | U                                                                                                                                                                                                            | 30                                      | 10 5        | EG0 (Reverse)                                 |                                |

|          |   | (1) 0 is connected to                           | o V <sub>cc</sub>                                                                                                                                                                                            |                                         |             |                                               |                                |

|          |   | (2) 1 is connected to                           | o V <sub>DDIO</sub>                                                                                                                                                                                          |                                         |             |                                               |                                |

|          |   |                                                 |                                                                                                                                                                                                              |                                         |             |                                               |                                |

| ROM[1:0] | I |                                                 |                                                                                                                                                                                                              |                                         |             | lect appropriate logic sect as shown in below | setting as described in table: |

|          |   | Table 4-5 : Chara                               | acter ROM                                                                                                                                                                                                    | l selection                             | 1           |                                               |                                |

|          |   |                                                 | ROM:                                                                                                                                                                                                         | 1 ROM                                   | ) ROI       | М                                             |                                |

|          |   |                                                 | 0                                                                                                                                                                                                            | 0                                       | A           |                                               |                                |

|          |   |                                                 | 0                                                                                                                                                                                                            | 1                                       | В           |                                               |                                |

|          |   |                                                 | 1                                                                                                                                                                                                            | 0                                       | С           |                                               |                                |

|          |   |                                                 | 1                                                                                                                                                                                                            | 1                                       | S/V         | / selectable (3)                              |                                |

|          |   | Note                                            |                                                                                                                                                                                                              |                                         |             |                                               |                                |

|          |   | (1) 0 is connected to (2) 1 is connected to     | o V <sub>SS</sub>                                                                                                                                                                                            |                                         |             |                                               |                                |

|          |   | (3) S/M/ selectable by                          | O V <sub>DDIO</sub>                                                                                                                                                                                          | command <sup>-</sup>                    | 72h "Eunch  | ion Selection B"; details                     | refer to                       |

|          |   | Table <b>6-2</b> .                              | y exteriueu                                                                                                                                                                                                  | Command                                 | ZII FUIIC   | ion selection b, details                      | ה וכוכו נט                     |

|          |   | Table 0 2.                                      |                                                                                                                                                                                                              |                                         |             |                                               |                                |

| OPR[1:0] | I | This pin is used to                             | select the                                                                                                                                                                                                   | character r                             | umber of    | character generator.                          | Refer to Table 5-4 for         |

|          |   | details. OPR1 and                               |                                                                                                                                                                                                              |                                         |             |                                               |                                |

|          |   |                                                 |                                                                                                                                                                                                              |                                         |             |                                               |                                |

|          |   | Table 4-6 : Chara                               | acter RAM                                                                                                                                                                                                    | l selection                             | 1           |                                               |                                |

|          |   |                                                 | OPR1                                                                                                                                                                                                         | OPR0                                    | CGROM       | CGRAM                                         | <del>-</del>                   |

|          |   |                                                 | 1                                                                                                                                                                                                            | 1                                       | 256         | 0                                             |                                |

|          |   |                                                 | 0                                                                                                                                                                                                            | 1                                       | 248         | 8                                             |                                |

|          |   |                                                 | 1                                                                                                                                                                                                            | 0                                       | 250         | 6                                             |                                |

|          |   |                                                 | 0                                                                                                                                                                                                            | 0                                       | 240         | 8                                             |                                |

|          |   | Note                                            |                                                                                                                                                                                                              |                                         |             |                                               |                                |

|          |   | (1) 0 is connected to                           | o V <sub>SS</sub>                                                                                                                                                                                            |                                         |             |                                               |                                |

|          |   | (2) 1 is connected to V <sub>DDIO</sub>         |                                                                                                                                                                                                              |                                         |             |                                               |                                |

| Pin Name   | Pin Type | Description                                                                                                                                                                                                                                                                                                                                     |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO       | I/O      | It is a GPIO pin. Details refer to OLED command DCh.                                                                                                                                                                                                                                                                                            |

| VSL        | Р        | This is segment voltage (output low level) reference pin.                                                                                                                                                                                                                                                                                       |

|            |          | When external VSL is not used, this pin should be left open.                                                                                                                                                                                                                                                                                    |

|            |          | When external VSL is used, connect with resistor and diode to ground (details depend on application).                                                                                                                                                                                                                                           |

| CL         | I        | External clock input pin.                                                                                                                                                                                                                                                                                                                       |

|            |          | When internal clock is enable (i.e. pull HIGH in CLS pin), this pin is not used and should be connected to Ground.                                                                                                                                                                                                                              |

|            |          | When internal clock is disable (i.e. pull LOW is CLS pin), this pin is the external clock source input pin.                                                                                                                                                                                                                                     |

| CLS        | I        | Internal clock selection pin.                                                                                                                                                                                                                                                                                                                   |

|            |          | When this pin is pulled HIGH, internal oscillator is enabled (normal operation).                                                                                                                                                                                                                                                                |

|            |          | When this pin is pulled LOW, an external clock signal should be connected to CL.                                                                                                                                                                                                                                                                |

| CS#        | I        | This pin is the chip select input connecting to the MCU.                                                                                                                                                                                                                                                                                        |

|            |          | The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).                                                                                                                                                                                                                                                             |

|            |          | In $I^2C$ mode, this pin must connect to $V_{SS}$ .                                                                                                                                                                                                                                                                                             |

| RES#       | I        | This pin is reset signal input.                                                                                                                                                                                                                                                                                                                 |

|            |          | When the pin is pulled LOW, initialization of the chip is executed.<br>Keep this pin pull HIGH during normal operation.                                                                                                                                                                                                                         |

| D/C#       | I        | This pin is Data/Command control pin connecting to the MCU.                                                                                                                                                                                                                                                                                     |

|            |          | When the pin is pulled HIGH, the data at D[7:0] will be interpreted as data.                                                                                                                                                                                                                                                                    |

|            |          | When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register.                                                                                                                                                                                                                                                       |

|            |          | In $I^2$ C mode, this pin acts as SA0 for slave address selection.                                                                                                                                                                                                                                                                              |

|            |          | When serial interface is selected, this pin must be connected to $V_{\text{SS}}$ .                                                                                                                                                                                                                                                              |

| R/W# (WR#) | I        | This pin is read / write control input pin connecting to the MCU interface.                                                                                                                                                                                                                                                                     |

|            |          | When 6800 interface mode is selected, this pin will be used as Read/Write (R/W#) selection input. Read mode will be carried out when this pin is pulled HIGH and write mode when LOW.                                                                                                                                                           |

|            |          | When 8080 interface mode is selected, this pin will be the Write (WR#) input. Data write operation is initiated when this pin is pulled LOW and the chip is selected.                                                                                                                                                                           |

|            |          | When serial or ${ m I}^2{ m C}$ interface is selected, this pin must be connected to ${ m V}_{SS}$ .                                                                                                                                                                                                                                            |

| E (RD#)    | I        | This pin is MCU interface input.                                                                                                                                                                                                                                                                                                                |

|            |          | When 6800 interface mode is selected, this pin will be used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled HIGH and the chip is selected. When 8080 interface mode is selected, this pin receives the Read (RD#) signal. Read operation is initiated when this pin is pulled LOW and the chip is selected. |

|            |          | When serial or ${ m I}^2{ m C}$ interface is selected, this pin must be connected to ${ m V}_{SS}$ .                                                                                                                                                                                                                                            |

http://www.wisechip.com.tw

| Pin Name        | Pin Type | Description                                                                                                                                                                                                                             |

|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |          |                                                                                                                                                                                                                                         |

| D[7:0]          | I/O      | These pins are bi-directional data bus connecting to the MCU data bus.                                                                                                                                                                  |

|                 |          | Unused pins are recommended to tie LOW.                                                                                                                                                                                                 |

|                 |          | When serial interface mode is selected, D0 will be the serial clock input: SCLK; D1 will be the serial data input: SID and D2 will be the serial data output: SOD.                                                                      |

|                 |          | When $I^2C$ mode is selected, D2, D1 should be tied together and serve as $SDA_{out}$ , $SDA_{in}$ in application and D0 is the serial clock input, SCL.                                                                                |

| FR              | 0        | This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect. It should be kept NC if it is not used. Refer to Section 5.4 for details. |

| SEG0 ~<br>SEG99 | 0        | These pins provide the OLED segment driving signals. These pins are $V_{\text{SS}}$ state when display is OFF.                                                                                                                          |

| COM0 ~<br>COM31 | 0        | These pins provide the Common switch signals to the OLED panel. These pins are in high impedance state when display is OFF.                                                                                                             |

| C[1:0]          | -        | These pins are reserved. Nothing should be connected to these pins, nor are they connected together.                                                                                                                                    |

| TR[9:0]         | -        | These pins are reserved. Nothing should be connected to these pins, nor are they connected together.                                                                                                                                    |

6

### 5 Functional Block Descriptions

### 5.1 MCU Interface selection

US2066 has all four kinds of interface type with MCU:  $I^2C$ , serial, 4-bit bus and 8-bit bus. Different MCU modes can be set by hardware selection on BS[2:0] pins; refer to Table 4-2 for BS[2:0] setting. This chip MCU interface consists of 8 data pins and 5 control pins. The pin assignment at different interface mode is summarized in Table 5-1.

Table 5-1: MCU interface assignment under different bus interface mode

| Pin Name<br>Bus  | Data/C               | Data/Command Interface |    |         |    |                    |                   |      | Control Signal |      |      |      |      |

|------------------|----------------------|------------------------|----|---------|----|--------------------|-------------------|------|----------------|------|------|------|------|

| Interface        | D7                   | D6                     | D5 | D4      | D3 | D2                 | D1                | D0   | E              | R/W# | CS#  | D/C# | RES# |

| 4-bit 6800       |                      | D[7:4] Tie LOW         |    |         |    | E                  | R/W#              | CS#  | D/C#           | RES# |      |      |      |

| 4-bit 8080       | D[7:4] Tie L         |                        |    | Tie LO\ | N  |                    |                   | RD#  | WR#            | CS#  | D/C# | RES# |      |

| 8-bit 6800       | D[7:0]               |                        |    |         |    |                    | E                 | R/W# | CS#            | D/C# | RES# |      |      |

| 8-bit 8080       |                      | D[7:0]                 |    |         |    |                    | RD#               | WR#  | CS#            | D/C# | RES# |      |      |

| Serial Interface | Tie LOW SOD SID SCLK |                        |    |         |    | Tie LC             | W                 | CS#  | Tie LOW        | RES# |      |      |      |

| $I^2C$           | Tie LOV              | V                      |    |         |    | SDA <sub>OUT</sub> | SDA <sub>IN</sub> | SCL  | Tie LC         | )W   |      | SA0  | RES# |

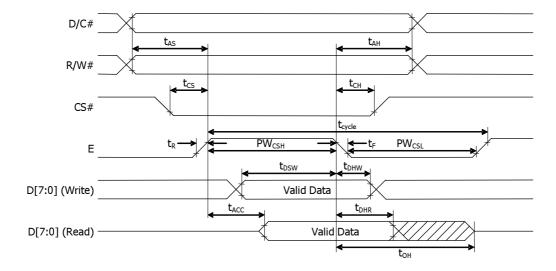

### 5.1.1 MCU Parallel 6800-series Interface

The parallel interface consists of 8 bi-directional data pins (D[7:0]), R/W#, D/C#, E and CS#.

A LOW in R/W# indicates WRITE operation and HIGH in R/W# indicates READ operation.

A LOW in D/C# indicates COMMAND read/write and HIGH in D/C# indicates DATA read/write.

The E input serves as data latch signal while CS# is LOW. Data is latched at the falling edge of E signal.

Table 5-2: Control pins of 6800 interface

| Function      | E             | R/W<br># | CS# | D/C# |

|---------------|---------------|----------|-----|------|

| Write command | $\rightarrow$ | L        | L   | L    |

| Read status   | $\downarrow$  | Н        | L   | L    |

| Write data    | $\downarrow$  | L        | L   | Н    |

| Read data     | $\downarrow$  | Н        | L   | Н    |

### Note

(1)

stands for falling edge of signal

H stands for HIGH in signal

L stands for LOW in signal

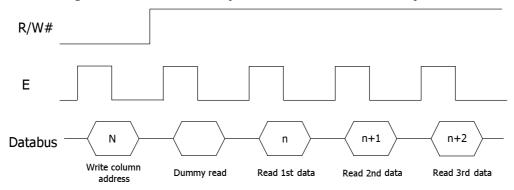

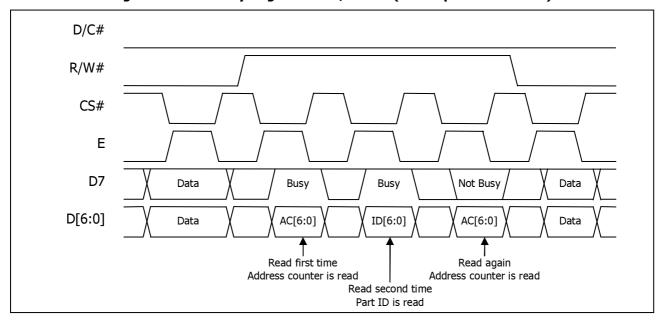

In order to match the operating frequency of display RAM with that of the microprocessor, some pipeline processing is internally performed which requires the insertion of a dummy read before the first actual display data read. This is shown in Figure 5-1.

Figure 5-1: Data read back procedure - insertion of dummy read

In case of 4-bit bus mode, data transfer is performed by two times to transfer 1 byte data.

When interfacing data length is 4-bit, only 4 ports, D[7:4], are used as data bus; the unused 4 ports, D[3:0] are recommended to tie to GND.

At first higher 4-bit (in case of 8-bit bus mode, the contents of D4 - D7) are transferred, and then lower 4-bit (in case of 8-bit bus mode, the contents of D0 - D3) are transferred. So transfer is performed by two times.

When interfacing data length is 8-bit, transfer is performed at a time through 8 ports, from D[7:0].

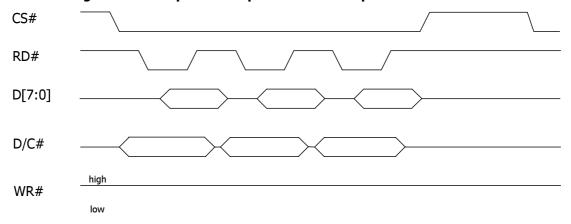

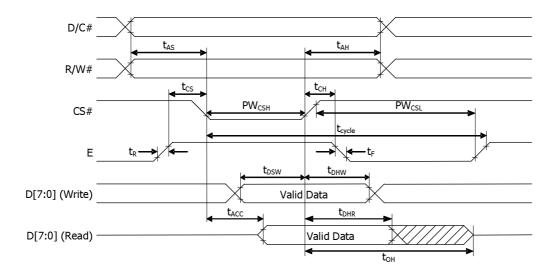

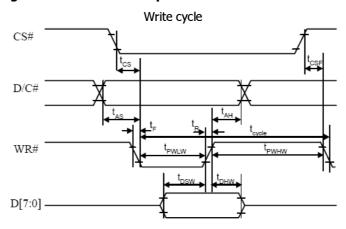

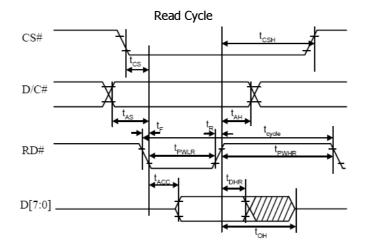

### 5.1.2 MCU Parallel 8080-series Interface

low

The parallel interface consists of 8 bi-directional data pins (D[7:0]), RD#, WR#, D/C# and CS#.

A LOW in D/C# indicates COMMAND read/write and HIGH in D/C# indicates DATA read/write. A rising edge of RD# input serves as a data READ latch signal while CS# is kept LOW. A rising edge of WR# input serves as a data/command WRITE latch signal while CS# is kept LOW.

CS#

WR#

D[7:0]

D/C#

high

Figure 5-2: Example of Write procedure in 8080 parallel interface mode

Table 5-3: Control pins of 8080 interface

| Function      | RD# | WR#      | CS# | D/C# |

|---------------|-----|----------|-----|------|

| Write command | Н   | <b>↑</b> | L   | L    |

| Read status   | 1   | Н        | L   | L    |

| Write data    | Н   | <b>↑</b> | L   | Н    |

| Read data     | 1   | Н        | L   | Н    |

### Note

(1) ↑ stands for rising edge of signal

(2) H stands for HIGH in signal

(3) L stands for LOW in signal

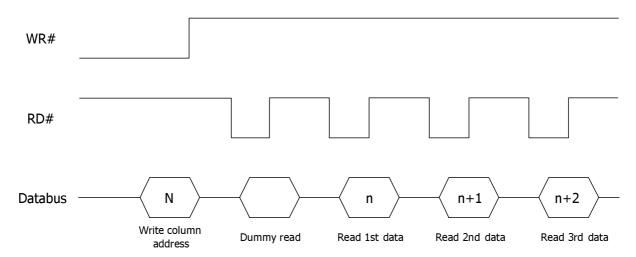

In order to match the operating frequency of display RAM with that of the microprocessor, some pipeline processing is internally performed which requires the insertion of a dummy read before the first actual display data read. This is shown in Figure 5-4.

Figure 5-4: Display data read back procedure - insertion of dummy read

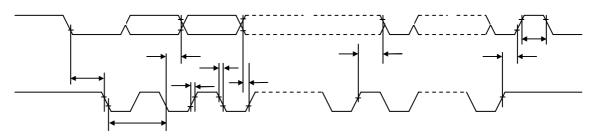

### 5.1.3 Serial Interface

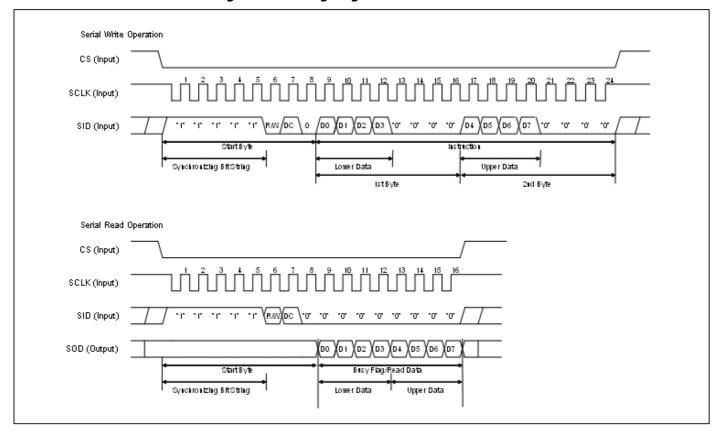

When serial interface mode is started, all the three ports, SCLK (synchronizing transfer clock; i.e. D0), SID (serial input data; i.e. D1), and SOD (serial output data; i.e. D2), are used. If US2066 is used with other chips, chip select port (CS#) can be used. By setting CS# to "Low", US2066 can receive SCLK input. If CS# is set to "High", US2066 resets the internal transfer counter.

Before transfer real data, start byte has to be transferred. It is composed of succeeding five "High" bits, read write control bit (R/W), register selection bit (DC) and end bit that indicates the end of start byte. Whenever succeeding five "High" bits are detected by US2066, it makes serial transfer counter reset and ready to receive next information.

The next input data are register selection bit that determine which register will be used, and read write control bit that determine the direction of data. Then end bit is transferred, which must have "Low" value to show the end of start byte. (Refer to Figure 5-5 and Figure 5-6).

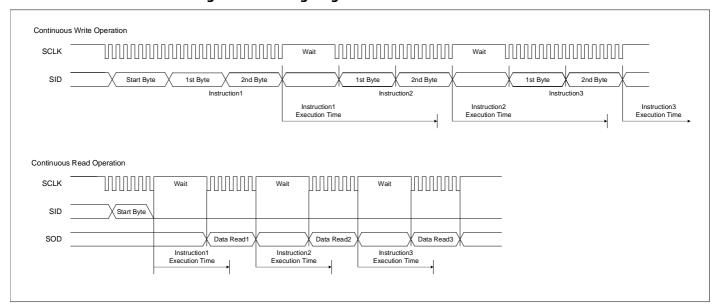

### 5.1.3.1 Write Operation (R/W = 0)

After start byte is transferred from MPU to US2066, 8-bit data is transferred which is divided into 2 bytes, each byte has four bit's real data and four bit's partition token data. For example, if real data is "10110001" (D0 - D7), then serially transferred data becomes "1011 0000 0001 0000" where the 2<sup>nd</sup> and the 4<sup>th</sup> four bits must be "0000" for safe transfer. To transfer several bytes continuously without changing D/C bit and R/W bit, start byte transfer is needed only at first starting time. Namely, after first start byte is transferred, real data can be transferred succeeding.

### 5.1.3.2 Read Operation (R/W = 1)

After start byte is transferred to US2066, MPU can receive 8-bit data through the SOD port at a time from the LSB. Wait time is needed to insert between start byte and data reading, because internal reading from RAM requires some delay. Continuous data reading is possible like serial write operation. It also needs only one start byte, **only if some delay between reading operations of each byte is inserted.** During the reading operation, US2066 observes succeeding five "High" from MPU. If it is detected, US2066 restarts serial operation at once and ready to receive DC bit. So in continuous reading operation, SID port must be "Low".

Figure 5-5: Timing Diagram of Serial Data Transfer

Figure 5-6: Timing Diagram of Continuous Data Transfer

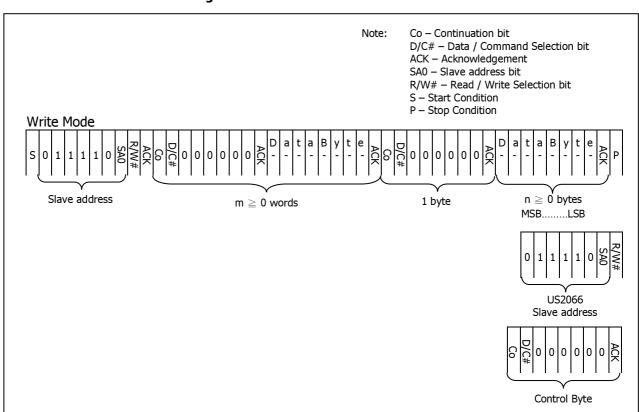

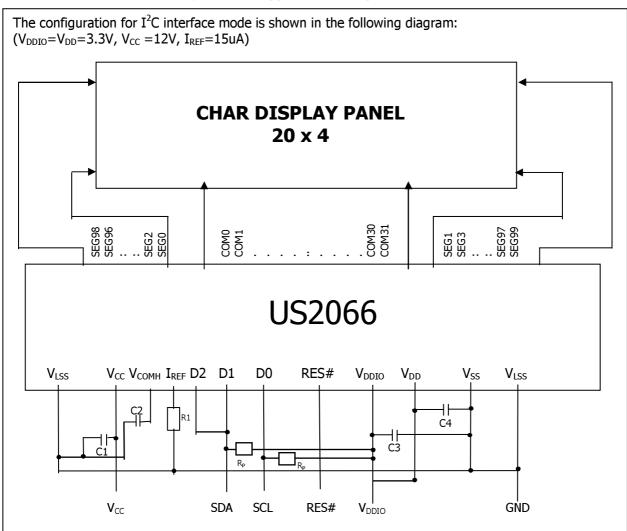

### **5.1.4** MCU I<sup>2</sup>C Interface

The  $I^2C$  communication interface consists of slave address bit SA0,  $I^2C$ -bus data signal SDA (SDA<sub>OUT</sub>/D<sub>2</sub> for output and SDA<sub>IN</sub>/D<sub>1</sub> for input) and  $I^2C$ -bus clock signal SCL (D<sub>0</sub>). Both the data and clock signals must be connected to pull-up resistors. RES# is used for the initialization of device.

a) Slave address bit (SA0)

US2066 has to recognize the slave address before transmitting or receiving any information by the  $I^2C$ -bus. The device will respond to the slave address following by the slave address bit ("SA0" bit) and the read/write select bit ("R/W#" bit) with the following byte format,

$b_7 \ b_6 \ b_5 \ b_4 \ b_3 \ b_2 \ b_1 \ b_0 \\ 0 \ 1 \ 1 \ 1 \ 1 \ 0 \ SA0 \ R/W\#$

"SA0" bit provides an extension bit for the slave address. Either "0111100" or "0111101" can be selected as the slave address of US2066. D/C# pin acts as SA0 for slave address selection.

"R/W#" bit is used to determine the operation mode of the  $I^2$ C-bus interface. R/W#=1, it is in read mode. R/W#=0, it is in write mode.

### b) I<sup>2</sup>C-bus data signal (SDA)

SDA acts as a communication channel between the transmitter and the receiver. The data and the acknowledgement are sent through the SDA.

It should be noticed that the ITO track resistance and the pulled-up resistance at "SDA" pin becomes a voltage potential divider. As a result, the acknowledgement would not be possible to attain a valid logic 0 level in "SDA".

"SDA $_{\rm IN}$ " and "SDA $_{\rm OUT}$ " are tied together and serve as SDA. The "SDA $_{\rm IN}$ " pin must be connected to act as SDA. The "SDA $_{\rm OUT}$ " pin may be disconnected. When "SDA $_{\rm OUT}$ " pin is disconnected, the acknowledgement signal will be ignored in the I $^2$ C-bus.

### c) I<sup>2</sup>C-bus clock signal (SCL)

The transmission of information in the  $I^2C$ -bus is following a clock signal, SCL. Each transmission of data bit is taken place during a single clock period of SCL.

### 5.1.4.1 I<sup>2</sup>C-bus Write data

The  $I^2C$ -bus interface gives access to write data and command into the device. Please refer to Figure 5-7 for the write mode of  $I^2C$ -bus in chronological order.

Figure 5-7: I<sup>2</sup>C-bus data format

http://www.wisechip.com.tw

### 5.1.4.2 Write mode for I2C

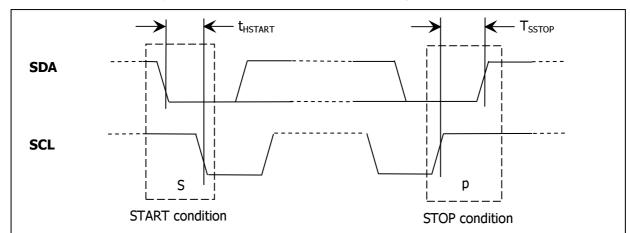

- 1) The master device initiates the data communication by a start condition. The definition of the start condition is shown in Figure 5-8. The start condition is established by pulling the SDA from HIGH to LOW while the SCL stays HIGH.

- 2) The slave address is following the start condition for recognition use. For the US2066, the slave address is either "b0111100" or "b0111101" by changing the SA0 to LOW or HIGH (D/C pin acts as SA0).

- The write mode is established by setting the R/W# bit to logic "0".

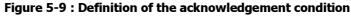

- 4) An acknowledgement signal will be generated after receiving one byte of data, including the slave address and the R/W# bit. Please refer to the Figure 5-9 for the graphical representation of the acknowledge signal. The acknowledge bit is defined as the SDA line is pulled down during the HIGH period of the acknowledgement related clock pulse.

- 5) After the transmission of the slave address, either the control byte or the data byte may be sent across the SDA. A control byte mainly consists of Co and D/C# bits following by six "0"'s.

- a. If the Co bit is set as logic "0", the transmission of the following information will contain data bytes only.

- o. The D/C# bit determines the next data byte is acted as a command or a data. If the D/C# bit is set to logic "0", it defines the following data byte as a command. If the D/C# bit is set to logic "1", it defines the following data byte as a data which will be stored at the DDRAM. The DDRAM address counter will be increased by one automatically after each data write.

- 6) Acknowledge bit will be generated after receiving each control byte or data byte.

- 7) The write mode will be finished when a stop condition is applied. The stop condition is also defined in Figure 5-8. The stop condition is established by pulling the "SDA in" from LOW to HIGH while the "SCL" stays HIGH.

Figure 5-8: Definition of the Start and Stop Condition

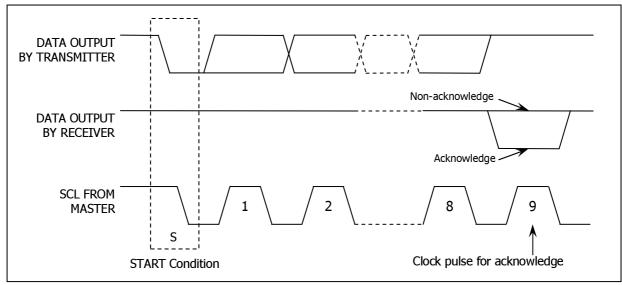

Please be noted that the transmission of the data bit has some limitations.

1. The data bit, which is transmitted during each SCL pulse, must keep at a stable state within the "HIGH" period of the clock pulse. Please refer to the Figure 5-10 for graphical representations. Except in start or stop conditions, the data line can be switched only when the SCL is LOW.

http://www.wisechip.com.tw

2. Both the data line (SDA) and the clock line (SCL) should be pulled up by external resistors.

Figure 5-10: Definition of the data transfer condition

### 5.2 Command Decoder

This module determines whether the input data is interpreted as data or command. Data is interpreted based upon the input of the D/C# pin.

If D/C# pin is HIGH, D[7:0] is interpreted as display data written to Character Generator RAM (CGRAM) or Display Data RAM (DDRAM). If it is LOW, the input at D[7:0] is interpreted as a command. Then data input will be decoded and written to the corresponding command register.

### **5.3 Oscillator Circuit and Display Time Generator**

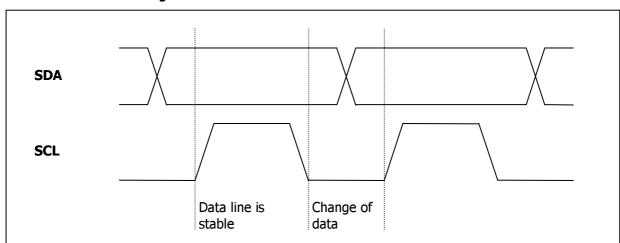

Figure 5-11: Oscillator Circuit and Display Time Generator

This module is an on-chip LOW power RC oscillator circuitry. The operation clock (CLK) can be generated either from internal oscillator or external source CL pin. This selection is done by CLS pin. If CLS pin is pulled HIGH, internal oscillator is chosen and CL should be connected to  $V_{SS}$ . Pulling CLS pin LOW disables internal oscillator and external clock must be connected to CL pins for proper operation. When the internal oscillator is selected, its output frequency Fosc can be changed by command D5h A[7:4].

The display clock (DCLK) for the Display Timing Generator is derived from CLK. The division factor "D" can be programmed from 1 to 16 by command D5h

$$DCLK = F_{OSC} / D$$

The frame frequency of display is determined by the following formula.

$$\boldsymbol{F}_{\text{FRM}} = \frac{\boldsymbol{F}_{\text{osc}}}{\boldsymbol{D} \times \boldsymbol{K} \times \boldsymbol{1} / \boldsymbol{Duty} \ \text{Ratio}}$$

, where

- D stands for clock divide ratio. It is set by command D5h A[3:0]. The divide ratio has the range from 1 to 16.

- K is the number of display clocks per row. The value is derived by

- K = Phase 1 period + Phase 2 period + K₀

- = 18 + 7 + 126 = 151 at power on reset (that is  $K_0$  is a constant that equals to 126)

- (Please refer to Section 5.5 "Segment Drivers / Common Drivers" for the details of the "Phase")

- Duty Ratio depends on display line number and segment-icon mode status. Refer to Table 2-1 for details.

- F<sub>OSC</sub> is the oscillator frequency. It can be changed by OLED command D5h A[7:4]. The higher the register setting results in higher frequency.

### 5.4 FR Synchronization

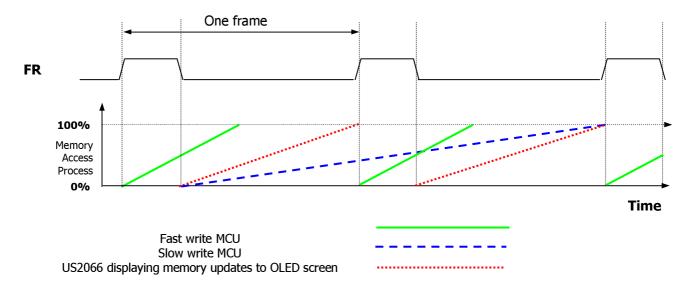

FR synchronization signal can be used to prevent tearing effect.

The starting time to write a new image to OLED driver is depended on the MCU writing speed. If MCU can finish writing a frame image within one frame period, it is classified as fast write MCU. For MCU needs longer writing time to complete (more than one frame but within two frames), it is a slow write one.

**For fast write MCU:** MCU should start to write new frame of ram data just after rising edge of FR pulse and should be finished well before the rising edge of the next FR pulse.

**For slow write MCU**: MCU should start to write new frame ram data after the falling edge of the  $1^{st}$  FR pulse and must be finished before the rising edge of the  $3^{rd}$  FR pulse.

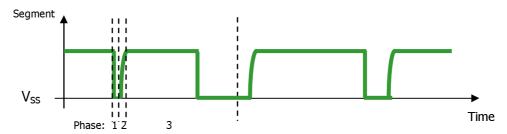

### 5.5 Segment Drivers / Common Drivers

Segment drivers deliver 100 current sources to drive the OLED panel. The driving current can be adjusted from 0 to 450uA with 256 steps. Common drivers generate voltage-scanning pulses.

The segment driving waveform is divided into three phases:

- 1. In phase 1, the OLED pixel charges of previous image are discharged in order to prepare for next image content display.

- 2. In phase 2, the OLED pixel is driven to the targeted voltage. The pixel is driven to attain the corresponding voltage level from  $V_{SS}$ . The period of phase 2 can be programmed in length from 1 to 15 DCLKs. If the capacitance value of the pixel of OLED panel is larger, a longer period is required to charge up the capacitor to reach the desired voltage.

- 3. In phase 3, the OLED driver switches to use current source to drive the OLED pixels and this is the current drive stage.

http://www.wisechip.com.tw

Figure 5-12: Segment Output Waveform in three phases

After finishing phase 3, the driver IC will go back to phase 1 to display the next row image data. This three-step cycle is run continuously to refresh image display on OLED panel.

### 5.6 SEG/COM Driving Block

This block is used to derive the incoming power sources into the different levels of internal use voltage and current.

- V<sub>CC</sub> is the most positive voltage supply.

- V<sub>COMH</sub> is the Common deselected level. It is internally regulated.

- V<sub>LSS</sub> is the ground path of the analog and panel current.

- $\bullet$  I<sub>REF</sub> is a reference current source for segment current drivers I<sub>SEG</sub>. The relationship between reference current and segment current of a color is:

$$I_{SEG} = (Contrast+1) / 8 x I_{REF}$$

in which the contrast (0~255) is set by OLED command "Set Contrast" 81h

The magnitude of  $I_{REF}$  is controlled by the value of resistor, which is connected between  $I_{REF}$  pin and  $V_{SS}$  as shown in Figure 5-13. It is recommended to set  $I_{REF}$  to 15 ± 2uA so as to achieve  $I_{SEG}$  = 450uA at maximum contrast 255.

Figure 5-13: I<sub>REF</sub> Current Setting by Resistor Value

Since the voltage at  $I_{REF}$  pin is  $V_{CC}$  –4.5V, the value of resistor R1 can be found as below:

For

$$I_{REF} = 15uA$$

,  $V_{CC} = 15V$ :

R1 = (Voltage at  $I_{REF} - V_{SS}$ ) /  $I_{REF}$

= (15 - 4.5) / 15uA

= 700k $\Omega$

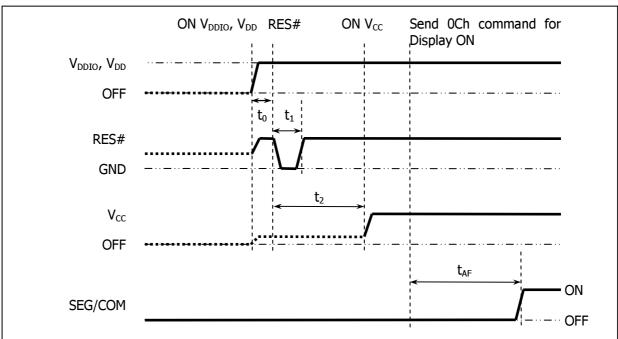

### 5.7 Power ON and OFF Sequence

The following figures illustrate the recommended power ON and power OFF sequence of US2066:

When LV I/O mode is chosen:

### Power ON sequence:

- 1. Power ON V<sub>DDIO</sub>, V<sub>DD</sub>

- 2. After  $V_{DDIO}$ ,  $V_{DD}$  become stable, set RES# pin LOW (logic low) for at least 3us  $(t_1)^{(4)}$  and then HIGH (logic high).

- 3. After set RES# pin LOW (logic low), wait for at least 100us ( $t_2$ ). Then Power ON  $V_{CC}$ .

- After V<sub>CC</sub> become stable, send fundamental command 0Ch (for RE=0b, SD=0b) for display ON. SEG/COM will be ON after 100ms (t<sub>AF</sub>).

Figure 5-14: The Power ON sequence.

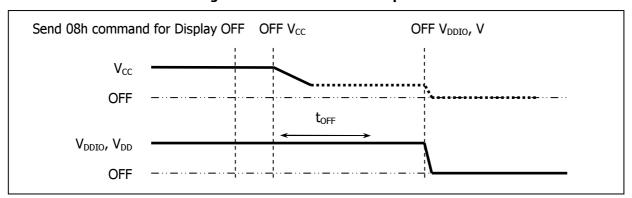

### Power OFF sequence:

- 1. Send fundamental command 08h (for RE=0b, SD=0b) for display OFF.

- Power OFF V<sub>CC</sub> (1), (2), (3)

- 3. Power OFF  $V_{DDIO}$ ,  $V_{DD}$  after  $t_{OFF}$ . (where Minimum  $t_{OFF}$ =0ms (5), Typical  $t_{OFF}$ =100ms)

Figure 5-15: The Power OFF sequence

### Note:

- $^{(1)}$  Since an ESD protection circuit is connected between  $V_{DDIO}$ ,  $V_{DD}$  and  $V_{CC}$ ,  $V_{CC}$  becomes lower than  $V_{DDIO}$ ,  $V_{DD}$  whenever  $V_{DDIO}$ ,  $V_{DD}$  is ON and  $V_{CC}$  is OFF as shown in the dotted line of  $V_{CC}$  in Figure 5-14 and Figure 5-15.

- (2) V<sub>CC</sub> should be kept float (i.e. disable) when it is OFF.

- <sup>(3)</sup> Power Pins ( $V_{DDIO}$ ,  $V_{DD}$ ,  $V_{CC}$ ) can never be pulled to ground under any circumstance.

- $^{(4)}$  The register values are reset after  $t_1$ .

- $^{(5)}$   $V_{DDIO}$ ,  $V_{DD}$  should not be Power OFF before  $V_{CC}$  Power OFF.

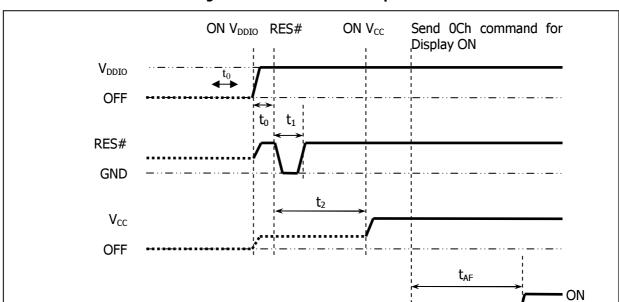

### When 5V I/O mode is chosen:

### Power ON sequence:

1. Power ON V<sub>DDIO</sub>

**OFF**

# WiseChip Semiconductor Inc.

- 2. After  $V_{DDIO}$  becomes stable, set wait time at least 1ms ( $t_0$ ) for internal  $V_{DD}$  become stable. Then set RES# pin LOW (logic low) for at least 3us ( $t_1$ ) (4) and then HIGH (logic high).

- 3. After set RES# pin LOW (logic low), wait for at least 100us (t<sub>2</sub>). Then Power ON V<sub>CC.</sub><sup>(1)</sup>

- After V<sub>CC</sub> become stable, send fundamental command 0Ch (for RE=0b, SD=0b) for display ON. SEG/COM will be ON after 200ms (t<sub>AF</sub>).

Figure 5-16: The Power ON sequence.

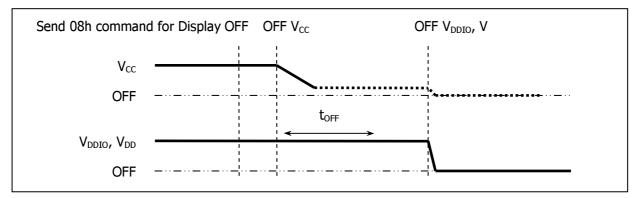

### Power OFF sequence:

- 1. Send fundamental command 08h (for RE=0b, SD=0b) for display OFF.

- 2. Power OFF V<sub>CC.</sub><sup>(1), (2), (3)</sup>

SEG/COM

3. Power OFF  $V_{DDIO}$  after  $t_{OFF}$ . (where Minimum  $t_{OFF}$ =0ms (5), Typical  $t_{OFF}$ =100ms)

Figure 5-17: The Power OFF sequence

### Note:

- $^{(1)}$  Since an ESD protection circuit is connected between  $V_{DDIO}$ ,  $V_{DD}$  and  $V_{CC}$ ,  $V_{CC}$  becomes lower than  $V_{DDIO}$ ,  $V_{DD}$  whenever  $V_{DDIO}$ ,  $V_{DD}$  is ON and  $V_{CC}$  is OFF as shown in the dotted line of  $V_{CC}$  in Figure 5-16 and Figure 5-17.

- (2) V<sub>CC</sub> should be kept float (i.e. disable) when it is OFF.

- $^{(3)}$  Power Pins ( $V_{DDIO}$ ,  $V_{DD}$ , and VCC) can never be pulled to ground under any circumstance.

- The register values are reset after  $t_1$ .

- $^{(5)}$   $V_{DDIO}$ ,  $V_{DD}$  should not be Power OFF before  $V_{CC}$  Power OFF.

http://www.wisechip.com.tw

### 5.8 Busy Flag (BF)

When BF = "High", it indicates that the internal operation is being processed. So during this time the next instruction cannot be accepted. BF can be read, when D/C# = Low and R/W# (WR#) = High (Read Instruction Operation), through D7. Before executing the next instruction, be sure that BF is not high.

### 5.9 Address Counter (AC)

Address Counter (AC) stores DDRAM and CGRAM address, transferred from Command Decoder After writing into (reading from) DDRAM and CGRAM, AC is automatically increased (decreased) by 1. In parallel and serial mode, when D/C# = Low and R/W# (WR#) = High, AC can be read through D[6:0].

### 5.10 Cursor/Blink Control Circuit

It controls cursor/blink ON/OFF and black/white inversion at cursor position.

### 5.11 Display Data Ram (DDRAM)

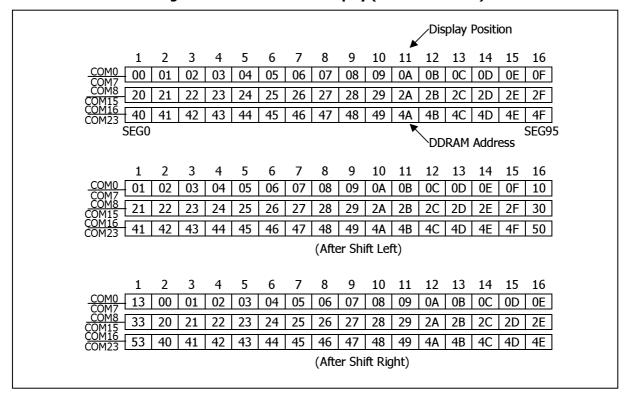

DDRAM stores display data of maximum 80 x 8 bits (80 characters). DDRAM address is set in the address counter (AC) as a hexadecimal number. (Refer to Figure 5-18)

Figure 5-18: DDRAM Address

| MSB |     |     |     |     |     | LSB |

|-----|-----|-----|-----|-----|-----|-----|

| AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

### **Display of 5-Dot Font Width Character**

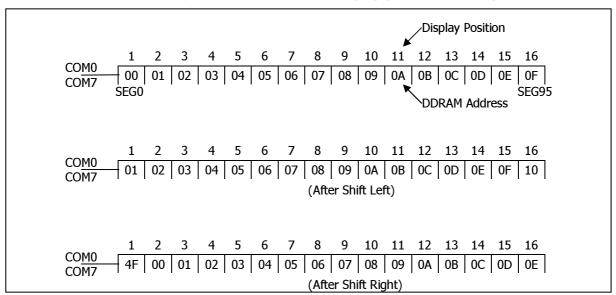

### 5-dot 1-line Display

In case of 1-line display with 5-dot font, the address range of DDRAM is 00H-4FH (Refer to Figure 5-19)

Figure 5-19: 1-line x 20ch. Display (5-dot Font Width)

### 5-dot 2-line Display

In case of 2-line display with 5-dot font, the address range of DDRAM is 00H-27H, 40H-67H (refer to Figure 5-20).

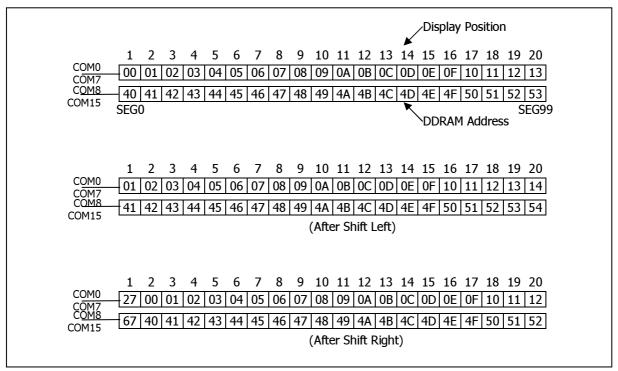

Figure 5-20: 2-line x 20ch. Display (5-dot Font Width)

### 5-dot 3-line Display

In case of 3-line display with 5-dot font, the address range of DDARM is 00H-13H, 20H-33H, 40H-53H (refer to Figure 5-21).

Figure 5-21: 3-line x 20ch. Display (5-dot Font Width)

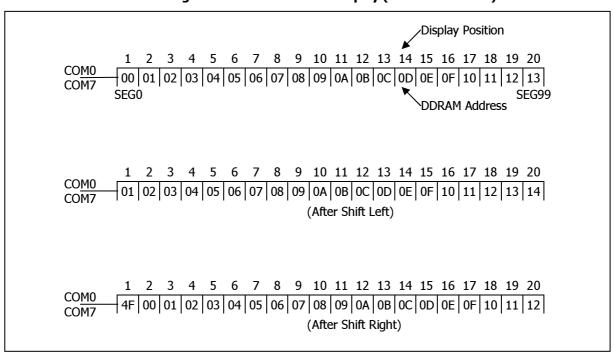

### 5-dot 4-line Display

In case of 4-line display with 5-dot font, the address range of DDARM is 00H-13H, 20H-33H, 40H-53H, 60H-73H (refer to

Figure 5-22).

Figure 5-22: 4-line x 20ch. Display (5-dot Font Width)

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 ← Display Position                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| COM0 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 - DDRAM Address                                                          |

| COM8 20 21 22 23 24 25 26 27 28 29 2A 2B 2C 2D 2E 2F 30 31 32 33                                                                          |

| COM16   40   41   42   43   44   45   46   47   48   49   4A   4B   4C   4D   4E   4F   50   51   52   53                                 |

| COM24<br>COM31   60   61   62   63   64   65   66   67   68   69   6A   6B   6C   6D   6E   6F   70   71   72   73  <br>SEG0 SEG99        |

| SEG0 SEG39                                                                                                                                |

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20                                                                                        |

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20<br>COM0 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 00                    |

| COM/ COM/ COM/ COM/ COM/ COM/ COM/ COM/                                                                                                   |

| COM15 21 22 23 24 25 26 27 28 29 2A 2B 2C 2D 2E 2F 30 31 32 33 20 COM16 COM23 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 40 |

| COM24<br>COM31 61 62 63 64 65 66 67 68 69 6A 6B 6C 6D 6E 6F 70 71 72 73 60                                                                |

| (After Shift Left)                                                                                                                        |

|                                                                                                                                           |

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20                                                                                        |

| COM0 13 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12                                                                          |

| COM15 33 20 21 22 23 24 25 26 27 28 29 2A 2B 2C 2D 2E 2F 30 31 32 COM16 53 40 42 42 42 45 45 45 47 49 49 49 49 45 45 50 51 52             |

| COM23 53 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 COM24                                                                   |

| COM31   73   60   61   62   63   64   65   66   67   68   69   6A   6B   6C   6D   6E   6F   70   71   72                                 |

| (After Shift Right)                                                                                                                       |

|                                                                                                                                           |

### **DISPLAY OF 6-DOT FONT WIDTH CHARACTER**

When the device is used in 6-dot font width mode, SEG96, SEG97, SEG98 and SEG99 must be opened.

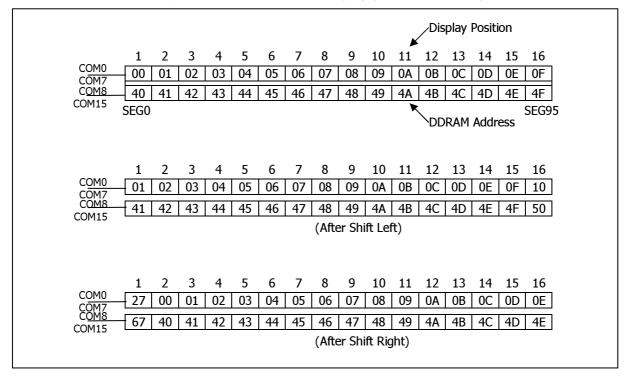

### 6-dot 1-line Display

In case of 1-line display with 6-dot font, the address range of DDRAM is 00H-4FH (refer to Figure 5-23).

Figure 5-23: 1-line x 16ch. Display (6-dot Font Width)

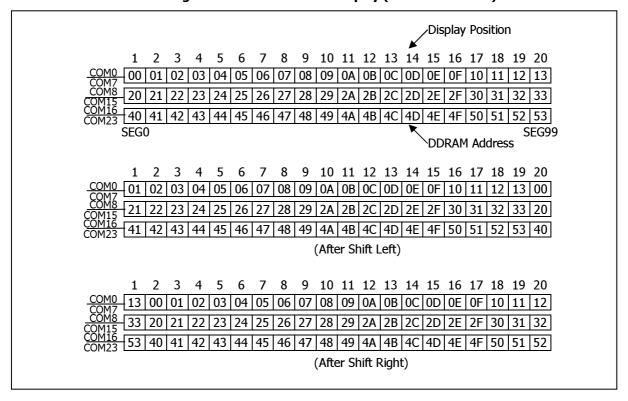

### 6-dot 2-line Display

In case of 2-line display with 6-dot font, the address range of DDRAM is 00H-27H, 40H-67H (refer to Figure 5-24).

Figure 5-24: 2-line x 16ch. Display (6-dot Font Width)

### 6-dot 3-line Display

In case of 3-line display with 6-dot font, the address range of DDARM is 00H-13H, 20H-33H, 40H-53H (refer to Figure 5-25).

Figure 5-25: 3-line x 16ch. Display (6-dot Font Width)

### 6-dot 4-line Display

In case of 4-line display with 6-dot font, the address range of DDARM is 00H-13H, 20H-33H, 40H-53H, 60H-73H (refer to Figure 5-26).

Figure 5-26: 4-line x 16ch. Display (6-dot Font Width)

| 1 2 3 4 5 6<br>COMO 00 01 02 03 04 05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7 8 9 10 11 12 13 14                  | 15 16 ← Display Position  OE OF ← DDRAM Address |